# A 20-MHz 0.323-mW 23.9-dBm-IIP3 4<sup>th</sup>-order Current-Reuse Lowpass Filter

Surachoke Thanapitak, Tatcha Chulajata, Pongsatorn Sedtheetorn

Department of Electrical Engineering

Mahidol University

Nakhon-Phatom, Thaialand

{surachoke.tha, tatcha.chu, pongsatorn.sed}@mahidol.ac.th

## Khaled Hayatleh

Faculty of Technology, Design and Environment

Oxford Brookes University

Wheatley Campus, Oxford

khayatleh@brookes.ac.uk

## Wanlop Surakampontorn

College of Advanced Manufacturing Innovation

King Mongkut's Institute of Technology Ladkrabang

Ladkrabang, Bangkok, Thailand

wanlop.ltpw@gmail.com

Abstract—A source follower lowpass filter which has a capability of bulk-attenuation cancellation in higher order is presented. Under strong inversion bias arrangement for high frequency application, this fourth-order-filter is simulated in a 0.18  $\mu$ m standard CMOS process and exhibits a 20 MHz bandwidth with total power consumption of 0.323 mW from 1.8 V supply. Third order intermodulation distortion verification with 1.9 and 2.1 MHz signal archives 23.9 dBm IIP3 with 75.5 dB dynamic range. By using figure-of-merit as a benchmark indicator, the proposed filter is one of the top in its class with the lowest power consumption.

Index Terms-Source Follower Filter, Low Power

#### I. Introduction

One of an important block which functions as a signal conditioning and extensively utilizes in telecommunication and sensor system is a filter. The requirement for filter design emphasizes low power consumption, high dynamic range (wide linear range with low noise) and small chip area. Source follower (SF) is one of an analog filter scheme which provides the aforementioned specifications from its compact structure, especially SF with high frequency (HF) application [1]–[5]

In this paper, a source follower with bulk neutralization (SFB) filter with body effect cancellation [6] which targeted for biomedical application is redesigned for high frequency signal filtering. The structure of this paper is organized as follows. In section II, the transfer function and other relevant design parameter of the filter is described. The pseudo-differential scheme of the proposed filter which benefits from wider linear range and common-mode feedback circuit exclusion is presented in section III. The simulation results in section IV reveal a high linearity (IIP3 = 23.9 dBm) and low power (0.323 mW).

#### II. PROPOSED HF BIQUAD FILTER

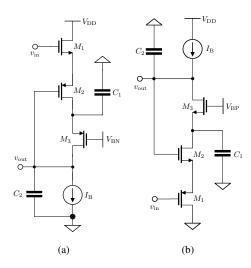

The second-order current-reuse filter from [6] which targets for high frequency application is shown in Fig. 1. For higher order filter implementation, the N-input biquad (Fig. 1(a)) and the P-input biquad (Fig. 1(b)) can be cascaded.

Fig. 1. (a) N-input and (b) P-input biquad filter.

The transfer function of these biquads is derived as in eq. (1) where  $g_{\rm mi}$  is the gate-only-transconductance and  $g_{\rm mti}$  is the gate-and-bulk-transconductance of each transistor. Under standard n-well CMOS process,  $g_{\rm mt1}=g_{m1}+g_{\rm mb1}$  and  $g_{\rm mt2}=g_{\rm m2}$  for the N-input biquad while  $g_{\rm mt1}=g_{m1}$  and  $g_{\rm mt2}=g_{\rm m2}+g_{\rm mb2}$  for P-input biquad where  $g_{\rm mbi}$  is the bulk transconductance.

$$\frac{v_{\text{out}}(s)}{v_{\text{in}}(s)} = \frac{g_{\text{m}1}g_{\text{mt}2}}{g_{\text{m}2}g_{\text{mt}1}} \cdot \frac{\frac{g_{\text{mt}1}g_{\text{m}2}g_{\text{mt}3}}{(g_{\text{mt}1}+g_{\text{mt}2})C_{1}C_{2}}}{\left(s^{2} + s\left(\frac{g_{\text{mt}3}}{C_{1}}\right) + \frac{g_{\text{mt}1}g_{\text{m}2}g_{\text{mt}3}}{(g_{\text{mt}1}+g_{\text{mt}2})C_{1}C_{2}}\right)}$$

RELEVANT FILTER DESIGN PARAMETERS.

|            | N-input                                                                                            | P-input                                                                                              |

|------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| K          | $rac{g_{ m m1}}{g_{ m mt1}}$                                                                      | $rac{g_{ m mt2}}{g_{ m m2}}$                                                                        |

| $\omega_o$ | $\sqrt{\frac{g_{ m mt1}g_{ m m2}g_{ m m3}}{C_1C_2(g_{ m mt1}+g_{ m m2})}}$                         | $\sqrt{\frac{g_{\rm m1}g_{\rm m2}g_{\rm mt3}}{C_1C_2[g_{\rm m1}+g_{\rm mt2}]}}$                      |

| Q          | $\sqrt{\frac{C_{1}g_{\text{m}1}g_{\text{m}2}}{C_{2}(g_{\text{m}1}+g_{\text{m}t2})g_{\text{m}t3}}}$ | $\sqrt{\frac{C_1 g_{\text{m}1} g_{\text{m}2}}{C_2 (g_{\text{m}1} + g_{\text{m}t2}) g_{\text{m}t3}}}$ |

The filter parameters for examples: pass-band gain (K), natural frequency  $(\omega_o)$  and quality factor (Q) can be extracted from eq.(1). Summary of these parameters is shown in Table I which reveals that the N-input biquad has gain attenuation due to bulk effect of the NMOS. Unexpectedly, the pass-band gain of the P-input biquad cancel out the gain loss from the N-input when these two biquas are cascaded.

# III. FOURTH-ORDER DIFFERENTIAL FILTER IMPLEMENTATION

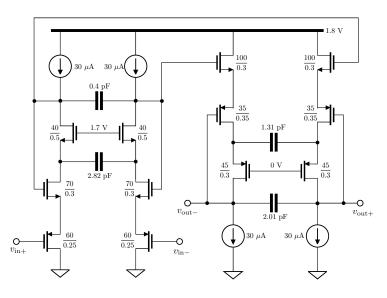

A fourth-order filter with pseudo-differential configuration is realized as shown in Fig. 2. The advantages of this arrangement is not only input linear range extension (even harmonics cancellation) but also capacitor area reduction by half (targeting at the same bandwidth as the single-ended scheme). The price to pay for this enhancement is higher power consumption and noise.

To minimize the input referred noise (IRN), the PMOS input biquad filter which provides higher passband gain is chosen as the first stage. With design target for HF application, this pseudo differential filter is biased with  $I_{\rm B}$  = 30  $\mu$ A to obtain 20 MHz bandwidth. The transconductance of each transistor and the quality factor of each stage are shown in Table II.

TABLE II 4<sup>th</sup>-order design parameters.

| Parameter                 | N-input | P-input |  |

|---------------------------|---------|---------|--|

| $g_{\rm m1}$ (mA/V)       | 0.493   | 0.504   |  |

| $g_{\mathrm{mb1}}$ (mA/V) | 0.097   | 0       |  |

| $g_{\mathrm{m}2}$ (mA/V)  | 0.339   | 0.61    |  |

| $g_{ m mb2}$ (mA/V)       | 0       | 0.012   |  |

| $g_{\mathrm{m}3}$ (mA/V)  | 0.368   | 0       |  |

| $g_{ m mb3}$ (mA/V)       | 0.56    | 0.01    |  |

| Q                         | 0.618   | 1.62    |  |

# IV. SIMULATION RESULTS

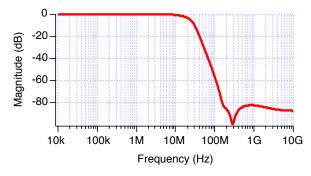

This proposed fourth-order lowpass filter is simulated in a 0.18  $\mu$ m standard CMOS process. The input DC common mode of the P-input stage is set as 300 mV. The total power consumption from the core filter and the bias current is 323  $\mu$ W under 1.8 V supply voltage. The frequency response of this proposed filter is shown in Fig. 3 which indicates 20 MHz bandwidth with 0-dB pass-band gain.

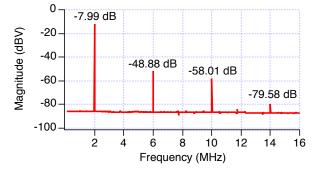

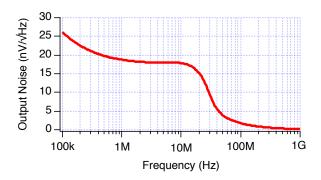

To determine the dynamic range (DR) of this proposed filter, the input linear range and input-referred noise (IRN) are calculated from Fig. 4 and 5, respectively. With 400 m $V_{\rm P}$  - 2 MHz sinusoidal signal, the output harmonic of this filter indicates a -40.89 dBc third harmonic distortion (HD3) as shown in Fig. 4. The output noise power spectral density (PSD) of this proposed filter as shown in Fig. 5 reveals 68.4  $\mu V_{\rm rms}$  IRN (integrating from 100 kHz to 20 MHz). As a result, the DR with 1% THD of this filter is 75.5 dB.

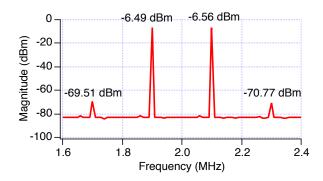

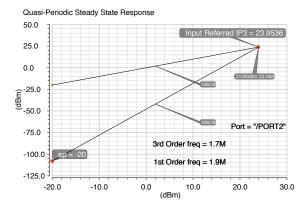

The input third-order intercept point (IIP3) is demonstrated by applying a two-tone sinusoidal signal (1.9 and 2.1 MHz) with -6.478 dBm (0.15  $V_P$ ) amplitude to this proposed filter. A -62.66 dBc third-harmonic intermodulation (IM3) is figured out as shown in Fig. 6. The relationship between IIP3 and IM3 [7] is

$$IIP3 = P_{in,dB} - (0.5 \times IM3_{dB}),$$

(2)

where  $P_{in,dB}$  is the input signal power. Subsequently, IIP3 of 24.85 dBm is calculated from eq. (2). To verify this calculation, IIP3 test under quasi-periodic steady state (QPSS) analysis is simulated with -20 dBm input power which concedes 23.95 dBm IIP3 as shown in Fig.

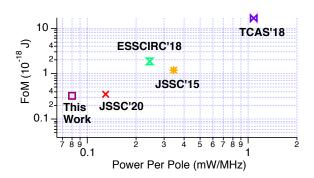

The performance comparison with other state-of-theart filters is summarized in Table III. This proposed passband gain compensation filter has the lowest power per pole among the recent works while a comparable high IIP3 as in [5] is achieved. To characterize the power, noise and linearity performance of a filter, a figure of merit is determined in two different aspects.

$$FoM = \frac{P_{DUT}/N}{f_{BW} \cdot SFDR \cdot N^{4/3}}$$

(3)

FoM =

$$\frac{P_{\text{DUT}}/N}{f_{\text{BW}} \cdot \text{SFDR} \cdot N^{4/3}}$$

(3)

FoM<sub>DR</sub> = DR +  $10 \cdot \log_{10} \left( \frac{f_{\text{BW}}}{P_{\text{DUT}}/N} \right)$  (4)

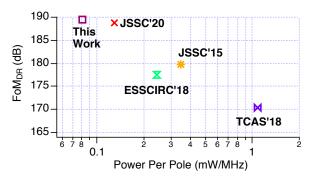

The first figure of merit (FoM) in eq. (3) [8] is emphasized on a spurious free dynamic range where  $P_{\text{DUT}}$  is the power consumption of the filter core circuit, N is the filter order,  $f_{\rm BW}$  is the filter -3dB bandwidth and SFDR =  $({\rm IIP3}/P_N)^{2/3}$  ( $P_N$  is the input-referred noise power). The other figure of merit (Fo $M_{DR}$ ) [1] which highlighted on the DR at 1 % THD is depicted in eq. (4). The FoM and FoM<sub>DR</sub> of this proposed filter are determined as shown in Table III. On benchmarking with other recent filter design, this filter has the best FoM and FoM<sub>DR</sub> (as shown in Fig. 8 and 9, respectively) while consuming power as half of [5].

## V. CONCLUSION

A source follower filter with 0-dB pass-band gain designed for HF application is verified in a standard CMOS process. Under pseudo differential configuration, this fourth-order LPF has a 20 MHz bandwidth under

Fig. 2. The proposed  $4^{\mathrm{th}}$ -order pseudo-differential filter with 30  $\mu\mathrm{A}$  bias current for HF application.

${\bf TABLE~III}\\ {\bf SUMMARY~AND~COMPARISON~WITH~OTHER~STATE-Of-The-ART~FILTERS}$

|                                             | This work | JSSC'20 [5] | JSSC'15 [2] | ESSCIRC'18 [3] | TCAS'18 [4] |

|---------------------------------------------|-----------|-------------|-------------|----------------|-------------|

| Technology                                  | 0.18 μm   | 0.18 μm     | 0.18 μm     | 28 nm          | 0.18 μm     |

| Architecture                                | SFB       | SF          | SSF         | FSF            | SC          |

| $V_{\mathrm{DD}}$ (V)                       | 1.8       | 1.3         | 1.8         | 1              | 1.8         |

| Filter order                                | 4         | 5           | 4           | 4              | 4           |

| Bandwidth (MHz)                             | 20        | 20          | 33          | 100            | 0.49-13.3   |

| Power (mW)                                  | 0.323     | 0.65        | 1.38        | 0.97           | 4.3         |

| Power per pole                              | 0.08075   | 0.13        | 0.345       | 0.2425         | 1.075       |

| DC Gain (dB)                                | 0         | 0           | -5          | -2.6           | 17.6        |

| V <sub>inTHD@-40dBc</sub> (V <sub>P</sub> ) | 0.4       | 0.675       | 0.225       | 0.16           | 0.1         |

| IIP3 (dBm)                                  | 23.98     | 24.5        | 18          | 12.5           | 11.1        |

| IRN $(nV_{rms}/\sqrt{Hz})$                  | 15.1      | 15.3        | 7.8         | 9.8            | 6.5         |

| DR @ THD -40 dBc (dB)                       | 75.5      | 76.9        | 70          | 61             | 74.9        |

| FoM (×10 <sup>-18</sup> · J)                | 0.32      | 0.36        | 1.2         | 1.9            | 16.9        |

| FoM <sub>DR</sub> (dB)                      | 189.4     | 188.7       | 179.8       | 177.5          | 170.4       |

Fig. 3. Frequency response of the proposed LPF when  $I_{\rm B}$  = 30  $\mu A$ .

Fig. 4. The harmonic component of this proposed filter when the 2 MHz - 400 mVp sinusoidal input is applied.

1.8 V supply and total current consumption of the filter core at 180  $\mu \rm A.$  The dynamic range of this filter

Fig. 5. The output noise characteristic of this proposed filter

Fig. 6. Inter Modulation Distortion (IMD) verification of this proposed filter when two tone input signal of 1.9 and 2.1 MHz is applied.

Fig. 7. A quasi-periodic steady state (QPSS) simulation of this proposed filter under -20 dBm input power.

Fig. 8. FoM plot vs. the power per pole of the filter.

Fig. 9.  $FoM_{\mathrm{DR}}$  plot vs. the power per pole of the filter

is examined with 400 m $V_{\rm P}$ -2 MHz sinusoidal signal which exhibits -40 dBc THD and 68.4  $\mu V_{\rm rms}$  IRN. Two-tone test with input signal of 1.9 and 2.1 MHz signal indicates 23.98 dBm IIP3.

#### REFERENCES

- [1] S. D'Amico, M. Conta and A. Baschirotto, "A 4.1-mW 10-MHz fourth-order Source-Follower-Based continuous-time filter with 79-dB DR", *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2713-2719, Dec. 2006.

- [2] M. De Matteis, A. Pezzotta, S. D'Amico and A. Baschirotto, "A 33 MHz 70 dB-SNR super-source-follower-based low-pass analog filter", *IEEE J. Solid-State Circuits*, vol. 50, no. 7, pp. 1516-1524, Jul. 2015.

- [3] F. Fary, M. De Matteis, T. Vergine and A. Baschirotto, "A 28 nm-CMOS 100 MHz 1 mW 12 dBm-IIP3 4th-order flipped-source-follower analog filter", *Proc. IEEE 44th Eur. Solid State Circuits Conf. (ESSCIRC)*, pp. 298-301, Sep. 2018.

[4] P. Payandehnia et al., "A 0.49 13.3 MHz tunable fourth-order

- [4] P. Payandehnia et al., "A 0.49 13.3 MHz tunable fourth-order LPF with complex poles achieving 28.7 dBm OIP3", *IEEE Trans. Circuits Syst. I Reg. Papers*, vol. 65, no. 8, pp. 2353-2364, Aug. 2018.

- [5] Y. Xu, H. Hu, J. Muhlestein and U. -K. Moon, "A 77-dB-DR 0.65-mW 20-MHz 5th-Order Coupled Source Followers Based Low-Pass Filter," in *IEEE Journal of Solid-State Circuits*, vol. 55, no. 10, pp. 2810-2818, Oct. 2020.

- [6] C. Sawigun and S. Thanapitak, "A Nanopower Biopotential Lowpass Filter Using Subthreshold Current-Reuse Biquads With Bulk Effect Self-Neutralization," in *IEEE Transactions on Cir*cuits and Systems I: Regular Papers, vol. 66, no. 5, pp. 1746-1757, May 2019

- [7] W. Sansen, Analog Design Essentials, Cham, Switzer-land:Springer, pp. 17-21, 2006.

- [8] T. Lo, C. Hung and M. Ismail, "A wide tuning range g<sub>m</sub>-C filter for multi-mode CMOS direct-conversion wireless receivers", *IEEE J. Solid-State Circuits*, vol. 44, no. 9, pp. 2515-2524, Sep. 2009