# Analysis and Design of High-Transconductance RF MOSFET Voltage-to-Current Converters

by

Ching-Mei Chen

School of Technology Oxford Brookes University

A thesis submitted in partial fulfilment of the requirements of Oxford Brookes University for the degree of

Doctor of Philosophy

October 2009

Acknowledgment

I would like to thank my director of research, Dr. Khaled Hayatleh, for his guidance

and support throughout the Ph.D. Dr. Hayatleh has dedicated a significant amount of

time, in a regular basis, on technical discussions with me and he was always been a

great source of advice and inspiration as well as psychological support during the

difficult period.

It has been a privilege as well as tremendous honour to learn a great deal from

Dr.Bryan Hart's wide experience in analogue circuit design.

Special thanks go to my second supervisor, Prof. John Lidgey for his positive

criticism and his support. His speaking and writing ability and his depth and speed of

technical mind were really valuable.

I would like to thank my parents, sister and brother for their continuous support.

Their love and faith in my abilities gave me the strength to complete this program. I

dedicate this work to them. It is the least that I could do to express my sincere

appreciation.

Finally special thanks are due to my dear friends: Qi Wang, Ke Chen, Dr. Ling Yang

and Koyn Hsiao for their long lasting support throughout this research work.

Ching-Mei Chen

Oxford Brookes University

Oxford

October 2009

i

## **Abstract**

The research described in this thesis is concerned with analysis and design of "High-Transconductance RF MOSFET Voltage-to-Current (V-I) Converters". Various V-I converter circuits published in the past have been reviewed by the author in order to understand the different techniques employed to improve transconductance (G<sub>t</sub>), linear operating range and total harmonic distortion (THD). Throughout this research, the emphasis has been to improve the above mentioned parameters. All the V-I converter circuits reported have been simulated using PSPICE and the results compared with the values obtained by theoretical analysis. Some of the results of this work have been already reported by the author in the technical literature. (See Chapter 9, at the end of this thesis, where reference to two publications by the author is given.)

It was essential to obtain accurate CMOS device parameters values, such as Early Voltage, transconductance parameter ratios  $\mu$  ( $g_m/g_{ds}$ ),  $\chi$  ( $g_{mb}/g_m$ ) and inter-electrode capacitances, to facilitate the design the process. This was achieved using an extensive set of simulations for the transistor operating under different bias conditions. Furthermore, a measurement technique, thought to be novel, for the direct determination of the transconductance ratios  $\mu$  and  $\chi$  is proposed.

In the next part of the work several types of current mirror are compared against the standard current mirrors, using analytical and simulation methods. Furthermore several MOSFET V-I converter designs were critically reviewed to understand the various existing techniques and their limitations.

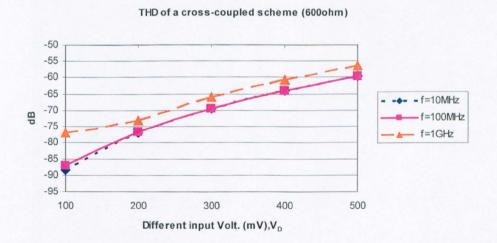

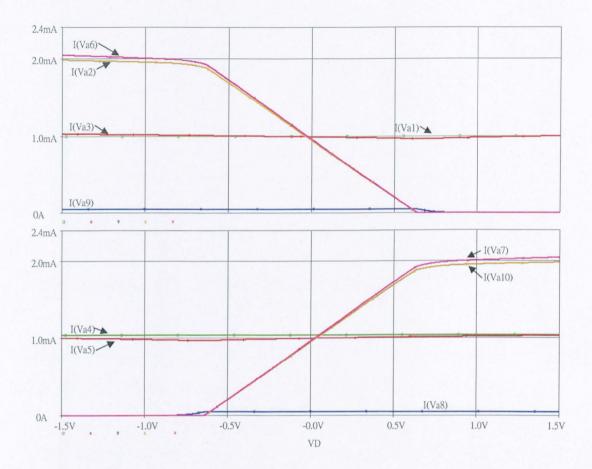

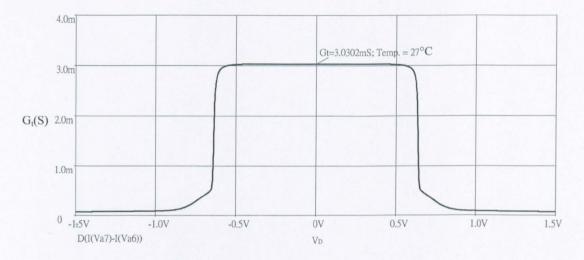

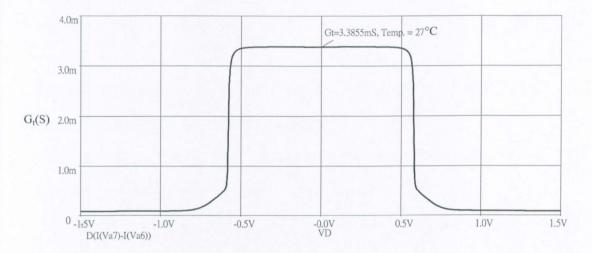

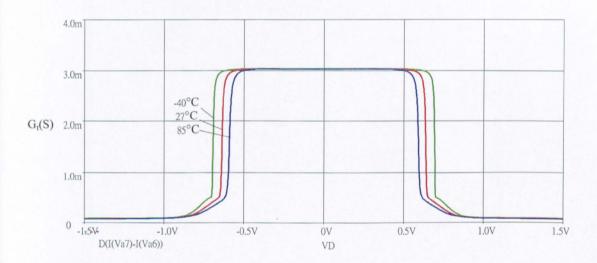

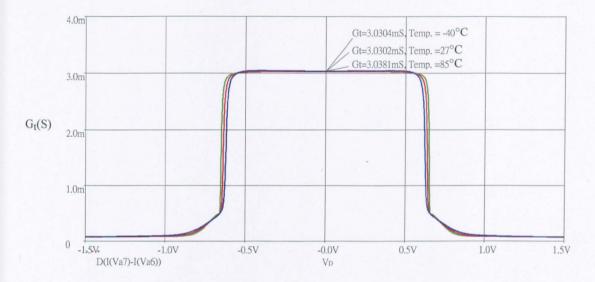

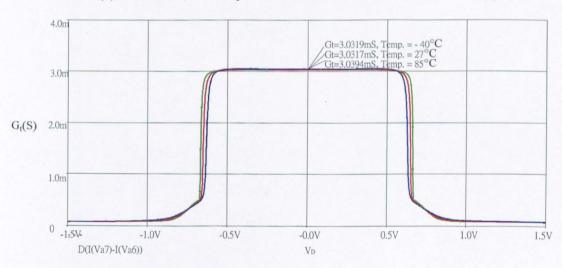

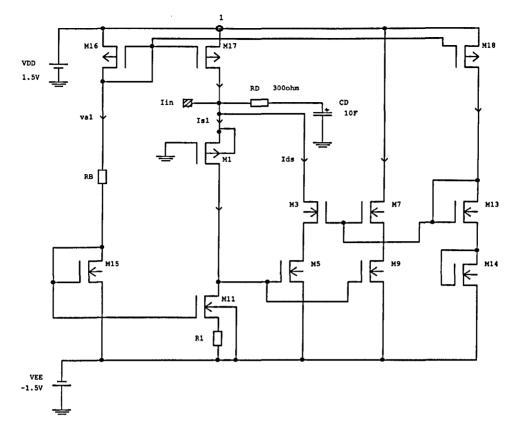

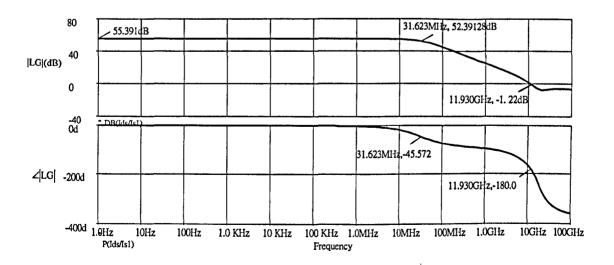

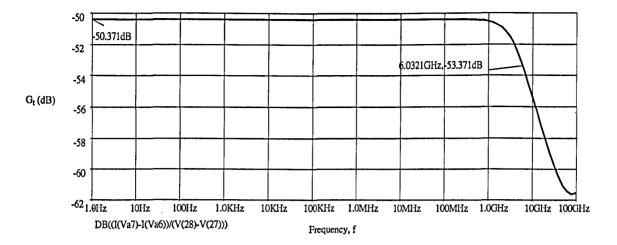

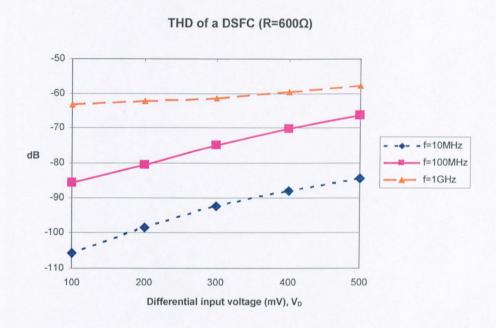

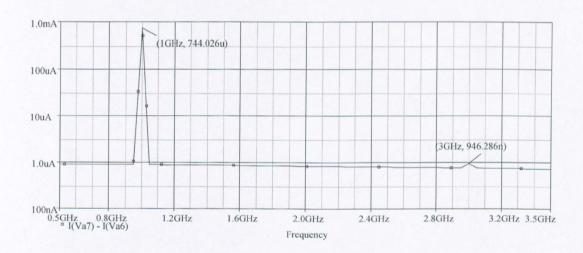

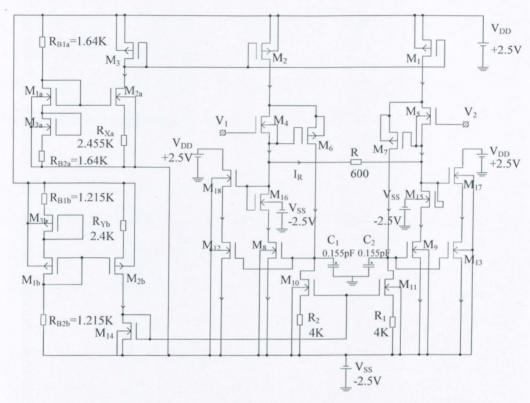

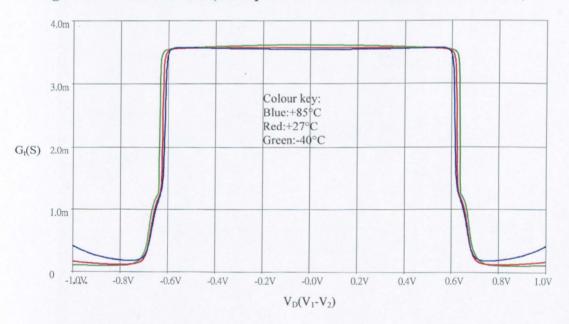

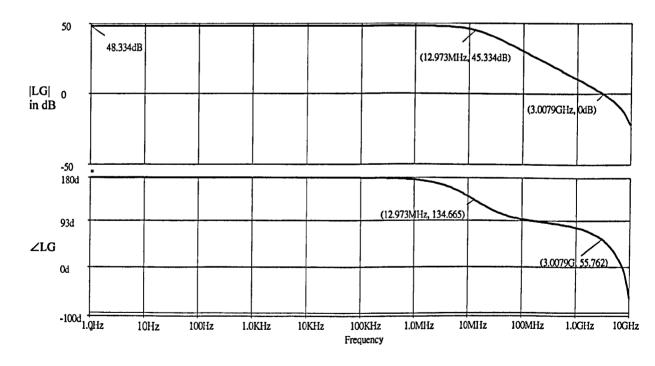

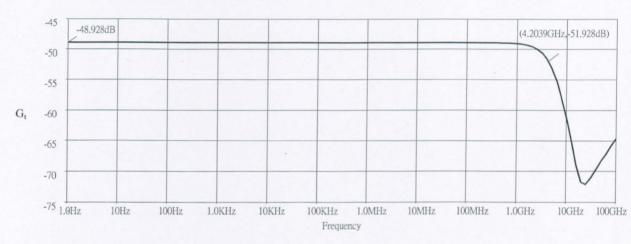

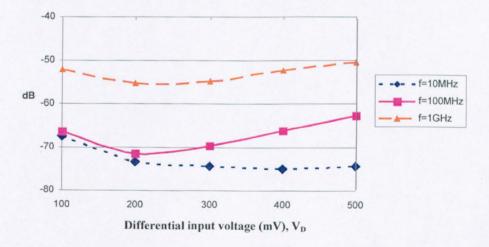

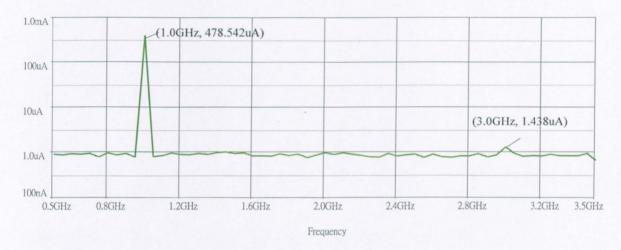

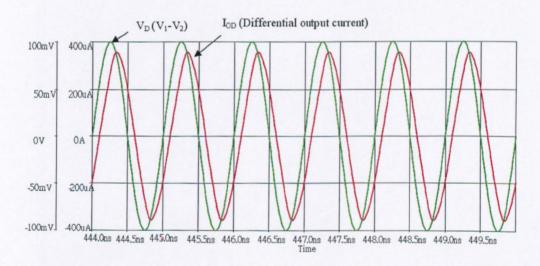

Two novel techniques, Drain-Source Feedback Circuits (DSFCs) and Drain-Gate Feedback Circuits (DGFCs) ere implemented with a new temperature-compensation scheme, designed to operate well in an industrial environment (-40°C  $\sim$  +85°C). It is found that the best types of V-I converters were the DSFCs which, offer a more accurate value of  $G_t$  (3.386mS) and the THD less than -57dB for a differential input operating range 500mV at 1GHz with a 3V total rail voltage. The DGFC circuits were also meet the initial design targets, the value of THD is less then -50dB, and operating in the Giga hertz frequency range is possible. Preliminary investigation on future work shows promising results.

# List of acronyms and principal MOSFET symbols

## Acronyms

CMOS Complementary Metal Oxide Silicon

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

THD Total Harmonic Distortion

V-I Voltage-to-Current

## **MOSFET symbols**

Av Voltage gain

β Transconductance parameter

$C_{db}$  Intrinsic Drain-Body capacitance  $C_{gd}$  Intrinsic Gate-Drain capacitance  $C_{gs}$  Intrinsic Gate-Source capacitance

f Frequency

$f_{-3dB}$  Cut-off frequency

$f_{\rm T}$  Transistor unity-gain frequency

g<sub>m</sub> Transconductance

g<sub>mb</sub> Body-effective transconductance

$G_{t,G_{m}}$  Transconductance

I<sub>D</sub> Drain current

λ Channel modulation factor

m Current mirror transfer ratio

r<sub>ds</sub> Small-signal drain-source resistance

r<sub>o</sub> Small-signal output resistance

V<sub>A</sub> Early Voltage

$V_{DS}$  Drain-Source Voltage  $V_{GS}$  Gate-Source Voltage

V<sub>SB</sub> Sourece-Substarte Voltage.

$V_T$  Threshold Volatge

# **Table of Contents**

| Acknowledgment                                                                                                       | 1    |

|----------------------------------------------------------------------------------------------------------------------|------|

| Abstract                                                                                                             | ii   |

| List of principal symbols and acronyms                                                                               | iii  |

| CHAPTER 1. THESIS INTRODUCTION                                                                                       | 1-1  |

| 1.1 Introducing the Voltage-to-Current Converter and its applications                                                | 1-2  |

| 1.2 Voltage-to-Current Converter design specifications                                                               | 1-4  |

| 1.3 Structure of the thesis                                                                                          | 1-5  |

| 1.4 References                                                                                                       | 1-7  |

| CHAPTER 2. DEVICE CHARACTERISATION                                                                                   | 2-1  |

| 2.1 Introduction                                                                                                     | 2-2  |

| 2.2 DC characteristics                                                                                               | 2-2  |

| 2.2.1 Background to the measurement                                                                                  | 2-2  |

| $2.2.2~\beta$ -factor and $V_T$ (Threshold Voltage) measurements                                                     | 2-4  |

| 2.2.3 Output characteristics                                                                                         | 2-7  |

| 2.2.4 $\mu$ (=g <sub>m</sub> /g <sub>ds</sub> ) and $\chi$ (=g <sub>mb</sub> /g <sub>m</sub> ) and their measurement | 2-15 |

| 2.2.4(a) μ measurement                                                                                               | 2-15 |

| 2.2.4(b) $\chi$ measurement                                                                                          | 2-21 |

| 2.2.4(c) Validation of parameter measurement techniques                                                              | 2-23 |

| 2.2.5 Inter-electrode capacitances                                                                                   | 2-25 |

| 2.2.5(a) Test1: Determination of $(C_{gs}+C_{gd})$                                                                   | 2-26 |

| 2.2.5(b) Test2: Determination of $(C_{gd}+C_{db})$                                                                   | 2-28 |

| 2.2.5(c) Test3: Determination of $(2C_{gs}+C_{gd}+C_{db})$                                                           | 2-30 |

| 2.2.5(d) Calculation of C <sub>gs</sub> , C <sub>gd</sub> , C <sub>db</sub> from tests                               | 2-32 |

| 2.3 Summary and Conclusions                                                                                          | 2-33 |

| 2.4 References                                                                                                       | 2-34 |

| 2.5 Appendix 2                                                                                                       |      |

| Appendix 2.1 MOSFET parameter relationships                                                                          | 2-36 |

|                                                                                                                      |      |

| Appendix 2.2 Analysis of $\mu$ measurement test circuit   | 2-39 |

|-----------------------------------------------------------|------|

| Appendix 2.3 Tabulated data for μ                         | 2-41 |

| Appendix 2.4 Tabulated data for χ                         | 2-42 |

| CHAPTER 3. DESIGN CONSIDERATIONS FOR BASIC                | 3-1  |

| SUB-CIRCUITS                                              |      |

| 3.1 Introduction                                          | 3-2  |

| 3.1(a) The simple current mirror (CM)                     | 3-2  |

| 3.1(b) The Widlar CM                                      | 3-7  |

| 3.2 Multi-transistor CMs                                  | 3-10 |

| 3.2.1 DC Characteristics                                  | 3-10 |

| 3.2.2 Incremental performance                             | 3-14 |

| 3.3 The Source-Follower                                   | 3-19 |

| 3.3.1 DC Characteristics                                  | 3-19 |

| 3.3.2 Incremental performance                             | 3-26 |

| 3.4 Summary and Conclusions                               | 3-30 |

| 3.5 References                                            | 3-33 |

| 3.6 Appendix 3                                            |      |

| Appendix 3.1 Output impedance of a 1:1 CM                 | 3-34 |

| Appendix 3.2 Source-Follower analysis                     | 3-37 |

| Appendix 3.3 Additional Source-Follower characteristics   | 3-41 |

| CHAPTER 4. A CRITICAL REVIEW OF EXISTING                  | 4-1  |

| V-I CONVERTER DESIGNS                                     |      |

| 4.1 Introduction                                          | 4-2  |

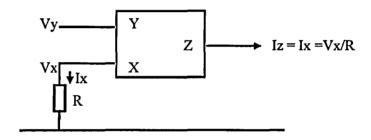

| 4.2 System-level approaches                               | 4-3  |

| 4.2.1 Type A (Using differential amps.)                   | 4-3  |

| 4.2.2 Type B (G <sub>t</sub> MOSFET-determined)           | 4-5  |

| 4.3 Limitations of Type B designs                         | 4-7  |

| 4.4 Type A development choices                            | 4-11 |

| 4.4.1 The differential amplifier with source degeneration | 4-11 |

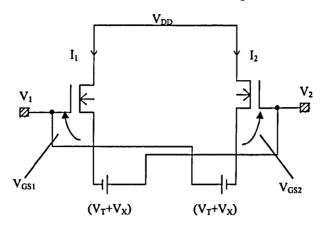

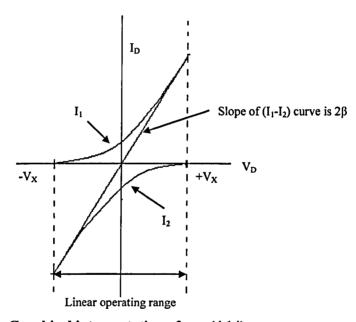

| 4.4.2 The cross-coupled scheme                            | 4-15 |

| 4.4.2 (a) Circuit implementation and operation                                 | 4-17          |

|--------------------------------------------------------------------------------|---------------|

| 4.4.2 (b) Limitations of the cross-coupled scheme                              | 4-23          |

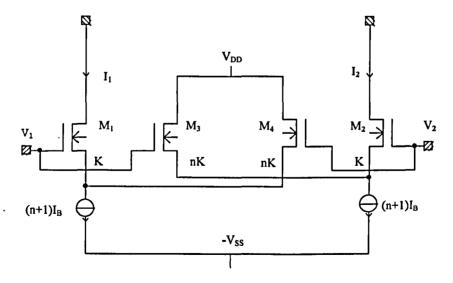

| 4.4.3 The current-feedback configuration                                       | 4-26          |

| 4.4.3 (a) Circuit implementation and operation                                 | 4-29          |

| 4.4.3 (b) Limitations of the current-feedback scheme                           | 4-33          |

| 4.5 Summary and Conclusions                                                    | 4-33          |

| 4.6 References                                                                 | 4-35          |

| 4.7 Appendix 4                                                                 |               |

| Appendix 4.1 A DC analysis of the current-feedback V-I                         | 4-37          |

| Appendix 4.2 Data for Total Harmonic Distortion of the cross-coupled scheme    | 4-39          |

| Appendix 4.3 Data for Total Harmonic Distortion of the current-feedback scheme | 4-40          |

| CHAPTER 5. DESIGN OF A V-I CONVERTER USING VOLTAGE                             | 5-1           |

| FOLLOWERS WITH DRAIN-SOURCE FEEDBACK                                           |               |

| 5.1 Introduction                                                               | 5-2           |

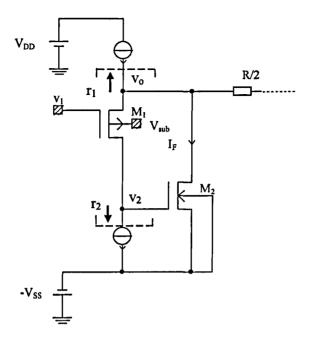

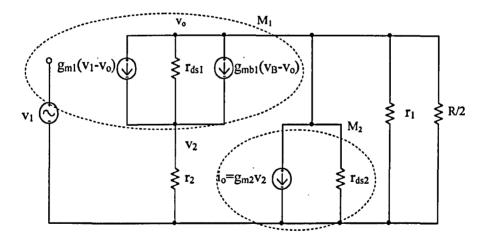

| 5.2 Half-circuit structure                                                     | 5-2           |

| 5.3 The proposed V-I in schematic form                                         | 5-5           |

| 5.3.1 Ideal circuit operation                                                  | 5-6           |

| 5.3.2 Calculation of non-ideal Gt                                              | 5-7           |

| 5.3.3 Design choices for a given specification                                 | 5-10          |

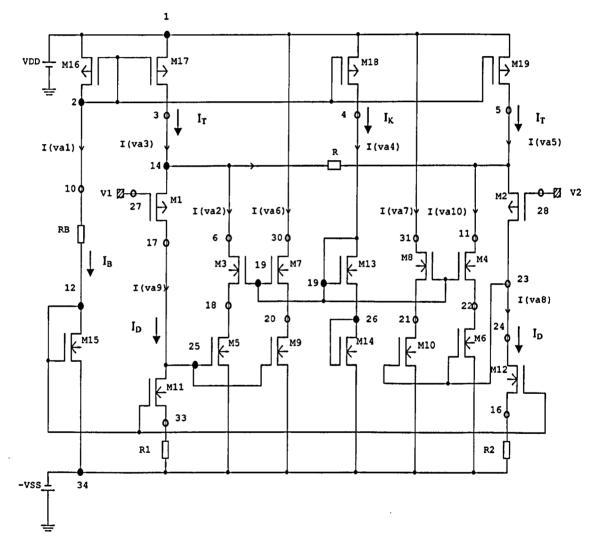

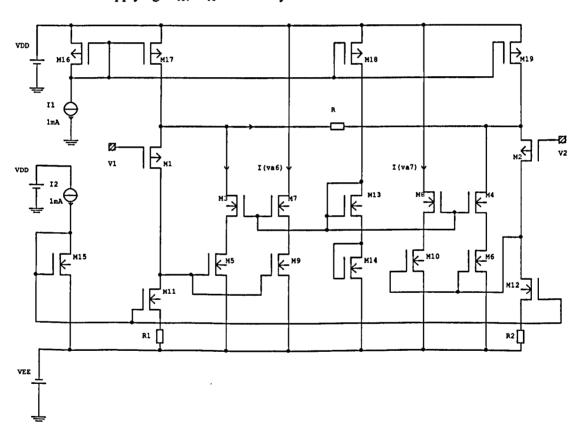

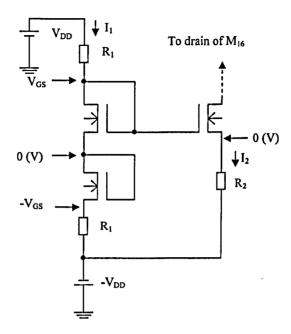

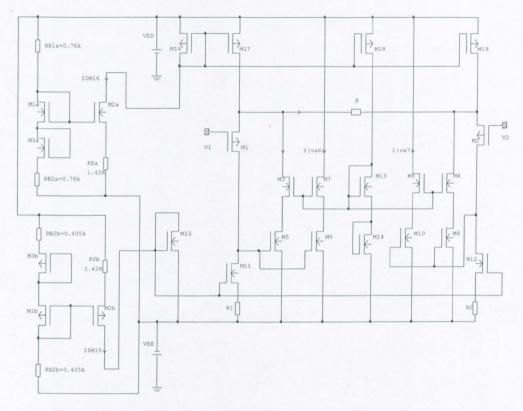

| 5.4 Circuit implementation                                                     | 5-12          |

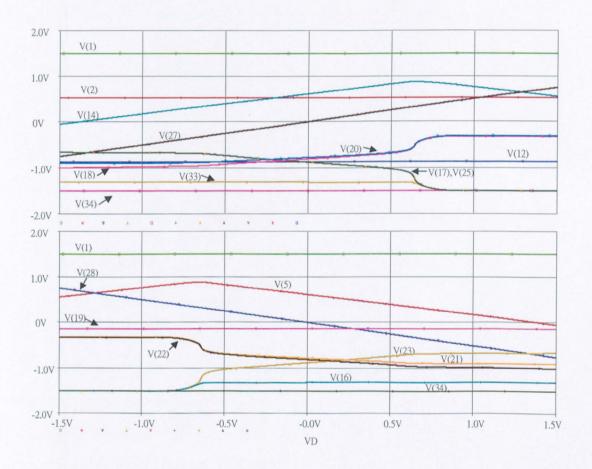

| 5.5 DC Conditions                                                              | 5-14          |

| 5.6 Small-signal high-frequency performance                                    | 5-26          |

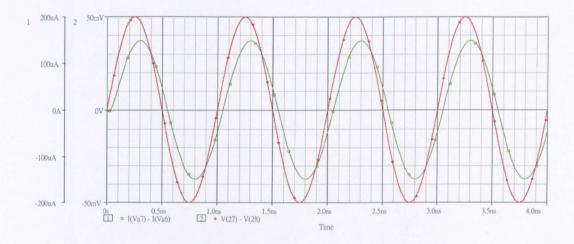

| 5.7 Distortion                                                                 | 5-25          |

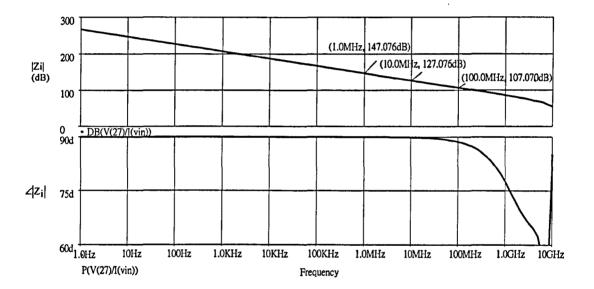

| 5.8 Terminal impedances                                                        | 5-27          |

| 5.9 Summary and Conclusions                                                    | 5 <b>-</b> 29 |

| 5.10 References                                                                | 5-31          |

| 5.11 Appendix 5                                                                |               |

| Appendix 5.1 D.C Conditions                                                    | 5-32          |

| Appendix 5.2 Theory of temperature compensation scheme                         | 5-33          |

| Appendix 5.3 THD data: spot figures                                            | 5-35          |

|                                                                                |               |

## CHAPTER 6. DESIGN OF A V-I CONVERTER USING VOLTAGE

| FOLLOWERS WITH DRAIN-GATE FEEDBACK                             | 6-1  |

|----------------------------------------------------------------|------|

| 6.1 Introduction                                               | 6-2  |

| 6.2 Evolution of the half-circuit structure                    | 6-2  |

| 6.3 The basic V-I converter type DGFC in schematic form        | 6-14 |

| 6.3.1 Ideal circuit operation                                  | 6-15 |

| 6.3.2 Non-ideal performance                                    | 6-16 |

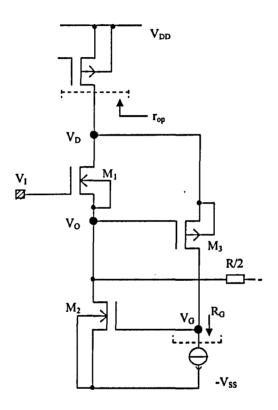

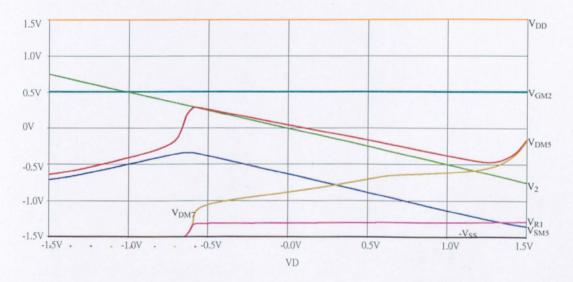

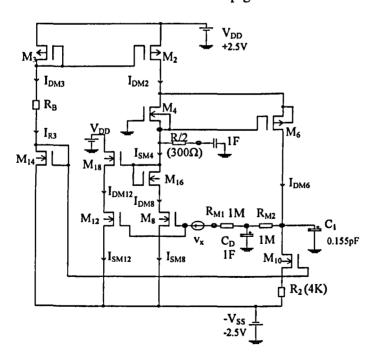

| 6.4 Circuit implementation of the DGFC1                        | 6-19 |

| 6.5 The DGFC2 and DGFC3                                        | 6-25 |

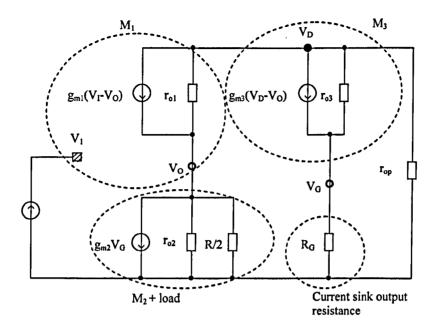

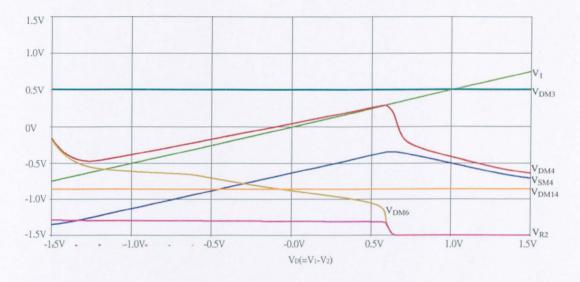

| 6.5.1 DC Conditions                                            | 6-28 |

| 6.5.2 Small-signal high-frequency performance                  | 6-32 |

| 6.5.3 Distortion                                               | 6-34 |

| 6.5.4 Terminal impedances                                      | 6-36 |

| 6.6 Summary and Conclusions                                    | 6-37 |

| 6.7 References                                                 | 6-39 |

| 6.8 Appendix 6                                                 |      |

| Appendix 6.1 Small-signal calculations for a half-circuit      | 6-40 |

| Appendix 6.2 DC conditions in the DGFC2 and DGFC3              | 6-47 |

| CHAPTER 7. CONCLUSIONS AND FUTURE WORK                         | 7-1  |

| 7.1 Conclusions                                                | 7-2  |

| 7.2 Future work                                                | 7-4  |

| 7.2.1 Circuit outline and problems                             | 7-5  |

| 7.3 References                                                 | 7-12 |

| 7.4 Appendix 7                                                 |      |

| Appendix 7.1 Proposed full circuit and preliminary performance | 7-13 |

# **CHAPTER 1**

# THESIS INTRODUCTION

- 1.1 Introducing the Voltage-to-Current Converter and its applications

- 1.2 Voltage-to-Current Converter design specifications

- 1.3 Structure of the thesis

- 1.4 References

# 1.1 Introducing the Voltage-to-Current Converter and its applications

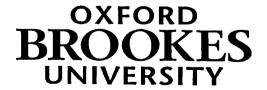

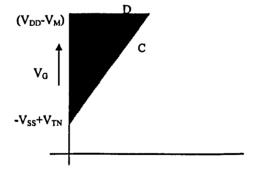

This thesis is concerned with Voltage-to-Current (V-I) converters, also referred to as Transconductors, usually referred to symbolically by either  $G_t$  or  $G_m$ . They are commonly used as active elements in analogue signal processing circuits, such as: filters, amplifiers, mixers and oscillators [1.1-1.4]. An ideal V-I converter should provide either a single-ended or a differential output current linearly proportional to the differential input voltage [1.5]. Fig.1.1(a) shows the ideal transfer function of a V-I converter and Fig.1.1(b) a simplified block diagram of a typical V-I converter.

Figure 1.1 (a) Ideal transfer function of a V-I converter

(b) A block diagram of a V-I converter

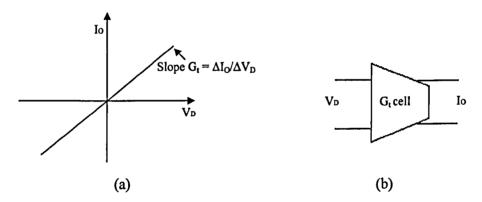

Figure 1.2 Typical V-I applications

- (a) G<sub>m</sub>-R variable gain amplifier

- (c) G<sub>m</sub>-C integrator filter

- (b) Active mixer with G<sub>m</sub> and switches

- (d) G<sub>m</sub>-LC filter

Fig.1.2 shows four typical applications using V-I converters, as shown in [1.3]. Fig.1.2(a) shows a V-I converter used as a voltage amplifier, where the gain of the amplifier is given by,

$$Av = \frac{V_O}{V_D} = G_m \cdot R \tag{1.1}$$

Clearly, varying either G<sub>m</sub> of R gives linear gain control.

Fig.1.2(b) is another application, used extensively in mixers as a part of a Radio Frequency (RF) circuit [1-6]. The maximum conversion gain of a conventional mixer for two square wave inputs is given by

$$Av = \frac{V_O}{V_D} = G_m \cdot 2/\pi \tag{1.2}$$

Fig.1.2(c) shows a typical integrator used in filters. The gain can be expressed by the following:

$$Av = \frac{V_O}{V_D} = \frac{1}{s(C/G_m)}$$

(1.3)

and a parallel inductor has been added in Fig 1.2(d) creating a 2nd-order band-pass filter for which the gain can be described as:

$$Av = \frac{V_O}{V_D} = G_m \cdot R_P \cdot \frac{\frac{s}{CR_P}}{\left(s^2 + \frac{s}{CR_p} + \frac{1}{LC}\right)}$$

(1.4)

where s is the complex frequency variables used in Laplace Transfer analysis.

### 1.2 Voltage-to-Current converter design specifications

The trends towards system-on-a-chip as well as mixed-mode (analogue and digital design) solutions mean that the majority of integrated circuit developments are undertaken in MOSFET. Also with the reducing feature size of modern high frequency CMOS transistors, these devices are now capable of matching and exceeding the ft of BJTs. With this in mind, the focus of this research work is on V-I converters designed for MOSFET implementation and the CMOS model for this research work is IBM 8RF\_DM 0.13µm technology. Table 1.1 gives the target parameters and values chosen to be used for all of the V-I converters designed and developed in this research work. In the interests of minimizing power dissipation and voltage rail supply levels, the maximum device-operating current was chosen to be 1mA and the rail supplies not to exceed 5V total.

This research work focuses on combining between high  $G_t$  and good linearity with a typical bias current of 1mA. The classical V-I converter is a long-tailed pair amplifier with source degeneration. The value of the source degeneration resistor determines both the  $G_t$  value and the linear range of input voltages. This work will focus on discussion of determining the value of resistance we used. The most optimistic linear range of operation that could be achieved would be  $\pm 500 \text{mV}$  and the transconductance value to be obtained for the ideal case would be 3.33mS with a source degeneration resistance of  $600\Omega$  [1-7]. A THD should better than -50dB and

the temperature range has been set from -40°C to +85°C, this being the standard industrial range. The technology selected for all of the work in this thesis is enhancement CMOS.

Table 1.1 Target specification

|   | Parameters                | Values           |

|---|---------------------------|------------------|

| 1 | Total supply voltage      | 3V to 5V         |

| 2 | Linear range of operation | -500mV to +500mV |

| 3 | Typical transconductance  | 3.33mS           |

| 4 | THD                       | <-50dB at 1GHz   |

| 5 | Temperature range         | -40°C to +85°C   |

| 6 | Technology                | MOSFET(CMOS)     |

#### 1.3 Structure of the thesis

The thesis is divided into 7 chapters and, to make the reading straightforward, only the results of longer mathematical derivations are included in the relevant text, with the full working given in an appendix linked directly to the end of each chapter. In addition, chapter references are laid out at the end of each chapter as well as in a complete list in alphabetical order at the end of the thesis.

A detailed analysis of the transistor-models used throughout this research, is presented in Chapter 2. The process of developing a new circuit is supported by theoretical analysis. Unfortunately, analytical device model parameters are not easily obtained directly from simulation model parameters. A key part of this chapter is extraction of these model parameters from PSPICE device characteristics, at the particular operating conditions required for each design. It will be shown that a thorough analysis of these parameters is necessary for accurate design, based on 'hand-calculations', and several novel circuits of measuring the parameters of a single transistor are presented and analyzed in this chapter. Without them, in some conditions, the simulation results do not match the theoretical analysis.

In Chapter 3, a review of biasing techniques is included together with an introduction to current-biasing circuitry that has been chosen because of its superior performance over other similar configurations [1.8] and [1.9]. A critical review of the source follower [1.10], including analysis of both DC and small-signal conditions is presented. The theoretical performance described in Chapter 3 is developed further in Chapter 5, where a novel V-I circuit described.

A critical review of two existing MOSFET V-I converter techniques, [1.11-1.13], currently used to improve the linearity of differential V-I converters, is presented in Chapter 4. Both system level and transistor level V-I design implementations are included in this chapter. The operating principle of each of these techniques is reviewed, with examples of circuits, and a comparison made.

In Chapters 5 and 6 detailed circuits exemplifying each novel technique, described in Chapter 4, are presented with analysis and discussion of the results of simulation with respect to transconductance, linear range of operation, total harmonic distortion and frequency response.

Finally, the concluding chapter of the thesis, Chapter 7, contains an overview and reflection of the main body of work of the thesis, and outlines a circuit, thought to contain novel features, intended for future work.

Appended to the end of the thesis are conference and journal papers produced by the author on the various voltage-to-current converters described here-in.

### 1.4 References

- [1.1] Demosthenous A., 'Low-Voltage MOS Linear Transconductor/Squarer and Four-Quadrant Multiplier for Analog VLSI' IEEE Transactions on Circuits and Systems-I: Regular Papers, Vol.52, No.9, Sept.2005, pp.1721-1731.

- [1.2] Sánchez-Sinencio E. and Silva-Martínez J., 'CMOS transconductance amplifiers, architectures and active filters: a tutorial' IEE Proc.-Circuits Devices Syst., Vol.147, No.1, Feb.2000, pp.3-12.

- [1.3] Klumperink E. A. M., Louwsma S. M., Wienk G. J. M. and Nauta B., 'A CMOS Switched Transconductor Mixer', IEEE Journal of Solid-State Circuits, Vol.39, No.8, Aug.2004, pp.1231-1240.

- [1.4] Lin C. S., Wu P. S., Chang H. Y. and Wang H. 'A 9-50-GHz Gilbert-Cell Down-Conversion Mixer in 0.13-μm CMOS Technology' IEEE Microwave and Wireless Components Letters, Vol.16, No.5, May 2006, pp.293-295.

- [1.5] Toumazou C., Lidgey F. J. and Haigh D. G., 'Analogue IC design: the current-mode approach', Peter Peregrinus Ltd. London 1990, Chapter 5, pp.181-220.

- [1.6] Lee T. H., 'The Design of CMOS Radio-Frequency Integrated Circuits', Cambridge University Express, 2<sup>nd</sup> Edition, pp.319-322

- [1.7] Mathew M., 'Design and Development of Low Distortion Bipolar Voltage-to-Current Converters for RF Applications', Oxford Brookes University, PhD Thesis 2007, Chapter 4., pp 4-1~4-16

- [1.8] Gray P. R., Hurst P. J., Lewis S. H. and Meyer R. G., 'Analysis and Design of Analog Integrated Circuits', John Wiley & Sons, Inc., Fourth Edition, New York, 2001, pp. 253-277

- [1.9] Johns D, Martin K, 'Analog integrated circuit design', John Wiley & sons, New York,1997, pp.125-145.

- [1.10] Gray R. P., Hurst J. P., Lewis H. S., and Meyer G. R., 'Analysis and Design of Analog Integrated Circuits', John Wiley and Sons, 4<sup>th</sup> Edition, New York, 2001, Chapter 3 pp.195-197.

- [1.11] Toumazou C., Lidgey F. J. and Haigh D. G., 'Analogue IC design: the current-mode approach', Peter Peregrinus Ltd, London, 1990, Chapter 4, pp.154-157.

- [1.12] Lidgey F. J. and Hayatleh K., 'Are current conveyors finally coming of age?', Electronics World, Mar. 2000, pp.242-246.

- [1.13] Carvajal R.G., Ramírez-Angulo J., López-Martín A. J., Torralba A., Galán J. A. G., Carlosena A. and Chavero F. M., 'The Flipped Voltage Follower: A Useful Cell for Low-Voltage Low-Power Circuit Design' IEEE Transactions on Circuits and Systems-I: Regular Papers, Vol.52, No.7, Jul.2005, pp.1276-1291.

# **CHAPTER 2**

## **DEVICE CHARACTERISATION**

- 2.1 Introduction

- 2.2 DC characteristics

- 2.2.1 Background to the measurement

- 2.2.2  $\beta$ -factor and  $V_T$  (Threshold Voltage) measurements

- 2.2.3 Output characteristics

- 2.2.4  $\mu$ (= $g_m/g_{ds}$ ) and  $\chi$ (= $g_{mb}/g_m$ ) and their measurement

- 2.2.4(a) µ measurement

- 2.2.4(b)  $\chi$  measurement

- 2.2.4(c) Validation of parameter measurement techniques

- 2.2.5 Inter-electrode capacitances

- 2.2.5(a) Test1: Determination of  $(C_{gs}+C_{gd})$

- 2.2.5(b) Test2: Determination of  $(C_{gd}+C_{db})$

- 2.2.5(c) Test3: Determination of  $(2C_{gs}+C_{gd}+C_{db})$

- 2.2.5(d) Calculation of Cgs, Cgd, Cdb from tests

- 2.3 Summary

- 2.4 References

- 2.5 Appendix 2

- Appendix 2.1 MOSFET parameter relationships

- Appendix 2.2 Analysis of  $\mu$  measurement test circuit

- Appendix 2.3 Tabulated data for µ

- Appendix 2.4 Tabulated data for x

#### 2.1 Introduction

This chapter deals with the measurement, by simulation, of some of the parameters of the N and P short-channel (0.13 $\mu$ m) IBM BSIM3 model MOSFETs used in the circuits described in this thesis.

Much information is, of course, given in the SPICE files for the devices, but not always presented in a manner, such as pictorially, that makes it easy to use by a circuit designer for initial hand calculations for a proposed design.

In the interests of minimizing power dissipation and rail supply levels, the maximum device-operating current was chosen to be 1 mA and the rail supplies not to exceed 2.5V.

To minimize device areas, a device width of 10µm is used, as some preliminary circuit investigations revealed its suitability.

Wherever possible the information obtained from the measurements, whether DC or AC, is presented graphically.

#### 2.2 DC characteristics

#### 2.2.1 Background to the measurements

In analogue circuit design, operation is normally in the saturated region of the drain characteristics. For both N and P channel devices this corresponds to  $|V_{DS}| \ge |V_{GS}-V_T|$  where the symbols have their usual meanings. (See Appendix 2.1 for symbol definitions)

For an N channel device, operating in strong inversion, a first-order model that is good enough for hand calculation is [2.1].

$$I_{D} = \frac{\beta}{2} (V_{GS} - V_{T})^{2} (1 + \lambda V_{DS})$$

(2.1)

It follows from this that there is a separate family of curves for  $I_D$  vs. $V_{GS}$ , for each value of  $V_{DS}$ .

However, for standardisation purposes, and because measurements are required for low values of  $V_{DS}$ , these were made with  $|V_{GD}|$ =0, corresponding to the circuit condition in which a MOSFET is used as a 'diode'. This gives  $I_D$ ,  $V_{DS}$  curves that have a slightly larger  $V_{GS}$ , for a given  $I_D$ , than is the case for  $V_{DS} > V_{GS}$  and this gives data that errs on the safe side for circuit estimations of maximum likely gate-source voltage drops.

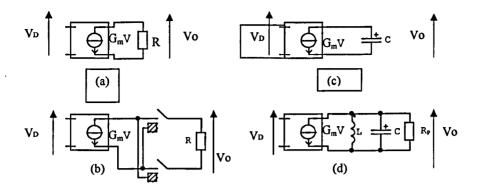

Figure 2.1 Test circuits for DC characteristics (a) NMOS (b) PMOS

The curves for  $I_D$  vs. $V_{GS}$  for given values of  $V_{SB}$  are useful for two reasons. They present, visually, useful information for design and they permit evaluation of the parameters  $\beta$  and  $V_T$  in eqn. (2.1)

This, from eqn. (2.1), the 'effective' value of  $\beta$  for  $V_{DG}=0$  is obtained from,

$$\sqrt{I_D} = \sqrt{\frac{\beta}{2}} (V_{GS} - V_T)$$

(2.2)

To the extent that eqn. (2.1) is applicable, a plot of  $\sqrt{I_D}$  versus  $V_{GS}$  should be a straight line with a slope  $\sqrt{\beta/2}$  and a projected back  $V_{GS}$  intercept for the effective of  $V_T$ , at each value of  $V_{SB}$ .

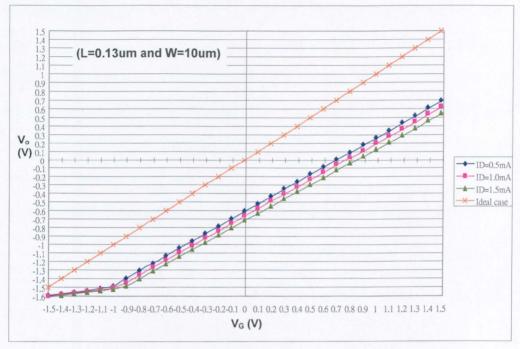

#### 2.2.2 Results

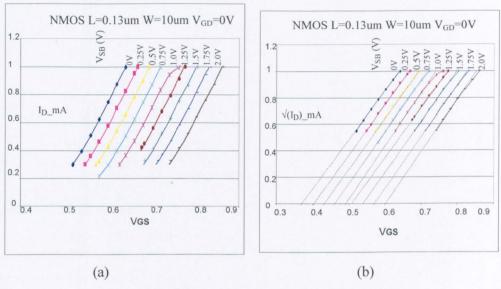

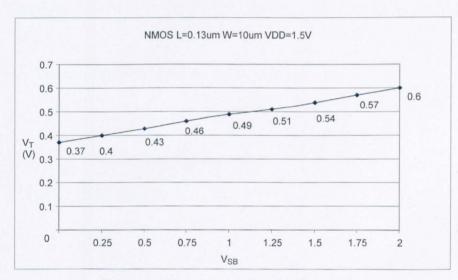

N channel results are presented in Figs2.2, 2.3 and Table1.1

Figure 2.2 DC Characteristics of NMOS

- (a) I<sub>D</sub> vs V<sub>GS</sub>

- (b)  $\sqrt{I_D}$  vs  $V_{GS}$

Figure 2.3 DC Characteristics for PMOS

- (a)  $|I_D|$  vs  $V_{GS}$

- (b)  $|\sqrt{I_D}| \ vs \ V_{GS}$

|      |        | $\beta  (\text{mA/V}^2)$ |        |       |

|------|--------|--------------------------|--------|-------|

| W(u) | VSB(V) | NMOS                     | VsB(V) | PMOS  |

| 10   | 0      | 28.657                   | -0     | 5.308 |

|      | 0.25   | 28.347                   | -0.25  | 5.103 |

|      | 0.5    | 28.298                   | -0.5   | 4.861 |

|      | 0.75   | 29.399                   | -0.75  | 4.715 |

|      | 1      | 24.611                   | -1     | 4.453 |

|      | 1.25   | 27.759                   | -1.25  | 4.212 |

|      | 1.5    | 28.297                   | -1.5   | 3.981 |

|      | 1.75   | 28.435                   | -1.75  | 3.76  |

|      | 2      | 28.532                   | -2     | 3.574 |

Table 2.1  $\beta$  as a function of  $V_{SB}$  (found from Fig. 2.2 and 2.3)

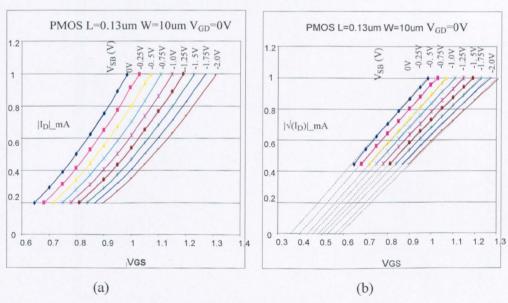

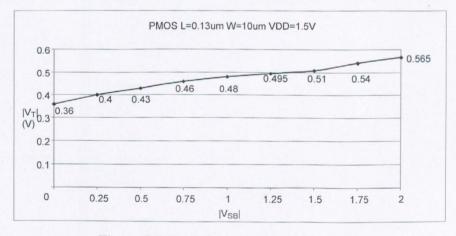

The variation of  $V_T(V)$  with  $V_{SB}(V)$  is shown in Fig.2.4

Figure 2.4 Variation of V<sub>T</sub> with V<sub>SB</sub>: N channel

Figure 2.5 Variation of  $|V_T|$  with  $|V_{SB}|$ : P channel

It is evident from Fig.2.2b and Table2.1 that for the case of the NMOS there is a straight line relationship between  $\sqrt{I_D}$  and  $V_{GS}$  over the simulated range and the lines are sensibly parallel indicating that  $\beta$  is, to a first order, independent of  $V_{SB}$ .

In Fig.2.3(b), for the PMOS device, there is also a straight line relationship between  $\sqrt{I_D}$  and  $|V_{GS}|$  but these lines are not parallel indicating a variation of  $\beta$  with  $V_{SB}$ .

Figs2.4, 2.5 show the variation of the threshold voltage  $V_T$  with  $V_{SB}$ .

Theoretically [2.2],

$$V_{T} = V_{T}(V_{SB} = 0) + \gamma \left( \sqrt{|2\phi_{F} + V_{SB}|} - \sqrt{|-2\phi_{F}|} \right)$$

(2.3)

However, in both cases there is an approximate linear relationship between  $V_T$  and  $V_{SB}$ .

In the case of the NMOS this is,

$$V_T(V) = 0.37 + \frac{(0.6 - 0.37)}{2} \cdot V_{SB}$$

or,

$$V_T(V) \cong 0.37 + (0.115) V_{SB}$$

(2.4)

For the PMOS the formula is,

$$V_T(V) \cong 0.36 + (0.103) V_{SB}$$

(2.5)

#### 2.2.3 Output Characteristics

Eqn.2.1 indicates that  $I_D$  depends on  $V_{DS}$ , as well as  $V_{GS}$ , but to proceed further and draw conclusions about the output incremental output resistance it is necessary to consider the nature of  $\lambda$ .

It is usually assumed that, in the saturated region of operation,  $\lambda$  is constant for a given  $V_{GS}$ .

This means that incremental output resistance is independent of V<sub>DS</sub>.

$$r_{ds} = \left(\frac{\partial V_{DS}}{\partial I_{D}}\right)\Big|_{V_{DQ}} = \frac{\left(1 + \lambda V_{DQ}\right)}{I_{D}\lambda}$$

(2.6)

The assumption  $\lambda \neq f(V_{DS})$  is based on experimental observation of the output characteristics of MOSFETs, operating over a  $V_{DS}$  range suitable for analogue applications, and a (limited) amount of theoretical reasoning based on device physical electronics.

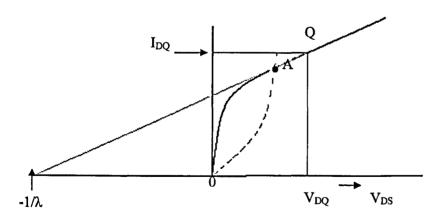

Fig.2.6 illustrates the approximation involved

Figure 2.6 Illustrating eqn (2.6) for  $\lambda \neq f(V_{DS})$  in the saturated region of an NMOS

The saturation region lies to the right of the dotted curve A for which the equation is

$$I_{\rm D} = \frac{\beta}{2} V_{\rm DS}^{2} . {(2.7)}$$

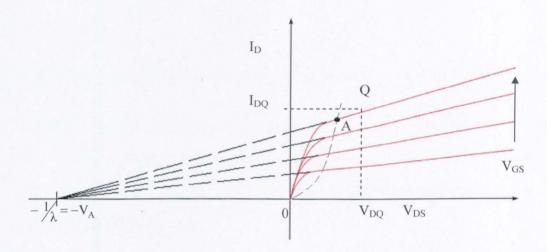

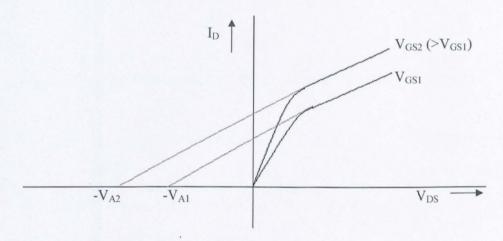

The next step, one made in a number of older textbooks (e.g., See [2.3]) is to assume not only that  $\lambda$  is independent of  $V_{DS}$  but also of  $V_{GS}$ , with the result that the characteristics have been presented in the manner shown is Fig.2.7.

Figure 2.7 Output characteristics for  $\lambda \neq f$  (VDS, VGS) in the saturated region related Fig. 2.11

The common intersection point  $V_{DS}$ = -1 /  $\lambda$  as been designated the Early Voltage, by analogy with the BJT parameter, and given the symbol  $V_A$ .

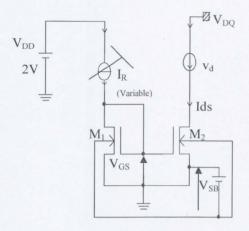

Simulation measurements were made at the output characteristics of an N channel MOSFET using the circuit of Fig.2.8

Figure 2.8 Circuit used to determine output characteristics of an NMOS

The reason for choosing this type of circuit rather than a amplifier for the common-source configuration is that it also supplies information on current –mirror operation described in the next chapter. A similar circuit, with reverse bias polarities, is applicable for P type MOSFETs.

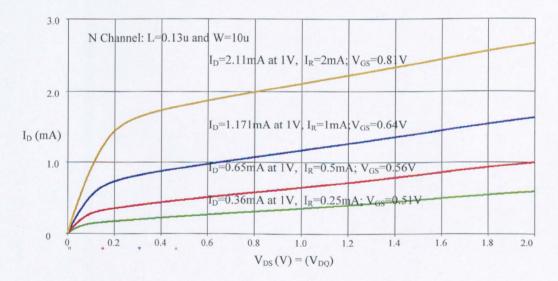

Figure 2.9 NMOS output characteristics for the circuit of Fig 2.8 with  $V_{SB}$ =0V. The data for each curve is given above it.

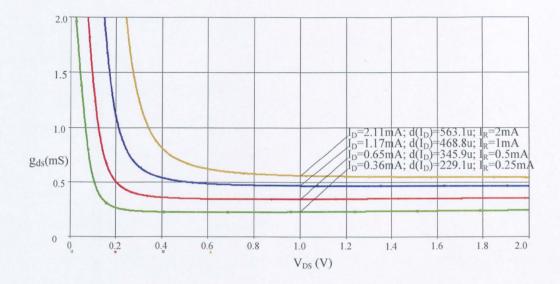

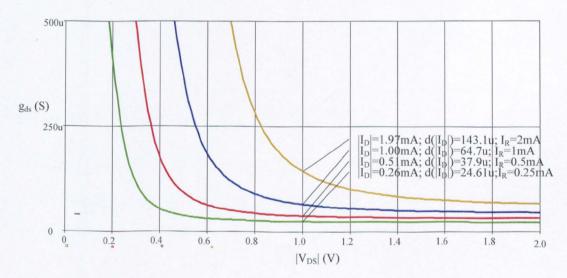

Figure 2.10 Incremental output conductance curves obtained from Fig 2.9

Figs2.9, 2.10 show the results of the simulation measurements and reveal unexpected features, which were confirmed by repetition, because they do not indicate a unique Early Voltage.

The DC characteristics of Fig.2.9 appear to show a linear dependence of  $I_D$  on  $V_{DS}$  for each value of  $V_{DS}$  (> 0.8V). Fig.2.10, showing  $g_{ds}$  as a function of  $V_{DS}$  for specified value of  $V_{GS}$ , confirms this because the resulting graphs are sensibly parallel to the  $V_{DS}$  axis for  $V_{DS} > 0.8V$ .

The variable slope of the curves for  $V_{DS} > 0.8V$  (approx.) is characteristic of operation of the MOSFET on the voltage-saturation region. What the graph set of Fig.2.9 does not confirm is the existence of the common intersection point, for tangents at a given  $V_{DS}$  when extrapolated back, on the negative  $V_{DS}$ , such as that shown in Fig.2.7, i.e., it does not prove that  $\lambda \neq f(V_{GS})$ .

For it to be so, it requires  $I_{DQ}$   $r_{ds}$  to be constant for all values of  $V_{GS}$ . To investigate the matter further the following calculations were made.

$I_R = 0.25 \text{ mA}$ :

$V_{A1} = [(1/229.1 \text{uA/V}) \times 0.36 \text{mA}] - 1 \text{V} = 0.57 \text{V}$

$I_R=0.5\text{mA}$ :

$V_{A2}=[(1/345.9 \text{ uA/V})\times 0.65\text{mA}]-1V=0.87V$

$I_R=1$ mA:

$V_{A3}=[(1/468.8 \text{ uA/V})\times 1.17\text{mA}]-1\text{V}=1.5\text{V}$

$I_R=2mA$ :

$V_{A4} = [(1/563.1 \text{ uA/V}) \times 2.11 \text{mA}] - 1 \text{V} = 2.75 \text{V}$

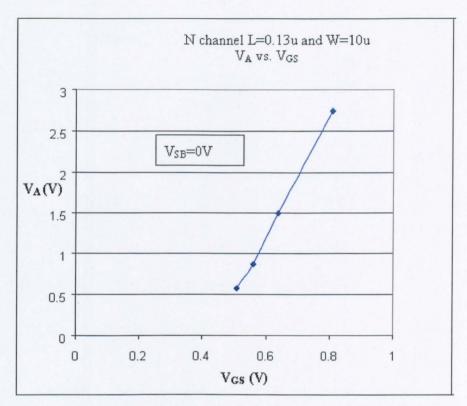

These results indicate that  $\lambda \neq f(V_{DS})$  for a given  $V_{GS}$  but  $\lambda = f(V_{GS})$ , a fact that is not apparent from a cursory inspection of Fig.2.9

Figure 2.11 Showing the implications of NMOS measurements

Fig.2.11 shows the implication of the measurements for just two values of  $V_{GS}$  and Fig.2.12 shows a plot of  $V_A$  vs. $V_{GS}$ .

Figure 2.12 Variation of Early Voltage, VA, with VGS for NMOS device

For first-order design calculations it is reasonable to assume  $V_A$  is linearly related to  $V_{GS}$ . The reason for this behaviour was not investigated because it involves the physical electronics of MOSFETs with sub-micron channel lengths and that was considered to be outside the scope of this thesis.

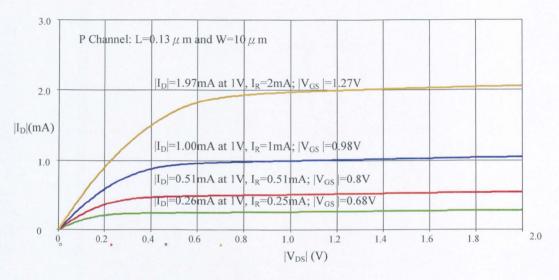

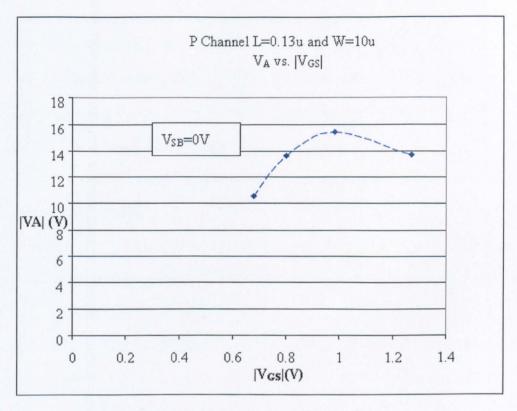

Comparison figures for Figs2.9, 2.10, 2.12 for the case of the PMOS are shown in Figs2.13, 2.14, 2.15 respectively.

Figure 2.13 PMOS output characteristics for V<sub>SB</sub>=0V

Figure 2.14 Incremental output characteristics curves obtained from Fig 2.13

Figure 2.15 Variation of  $|V_A|$  with  $|V_{GS}|$  for a PMOS device

Comparing Fig.2.15 with Fig.2.10 it is apparent that the PMOS device affects a lower output conductance than the NMOS, for a given  $I_R$ , but this requires a much larger  $|V_{GS}|$  (1.27V compared to 0.81V)

### 2.2.4 Transconductance ratios (g<sub>m</sub>/g<sub>ds</sub>) and (g<sub>mb</sub>/g<sub>m</sub>)

The transconductance ratios  $(g_m/g_{ds})$ , denoted by the symbol  $\mu$  (but without a subscript in order to distinguish it from the symbol for carrier mobility), and  $(g_{mb}/g_m)$ , denoted by the  $\chi$  [2.4], appear in the analysis and design of V-Is via the dependence of the latter on feedback amplifiers and current generators.

Parameter  $\mu$  characterises the theoretical maximum voltage gain of a single-stage common-source amplifier.

Parameter  $\chi$  sets a limit to the maximum theoretical voltage gain of a source-follower in which the substrate of the MOSFET used is not connected to its source terminal. Neither  $\mu$  nor  $\chi$  are specified in SPICE data.

A novel circuit method of determining their dependencies on DC bias conditions is presented in the next two sections. A third section validates the results obtained.

#### 2.2.4(a) µ measurements

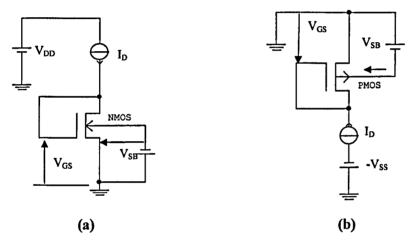

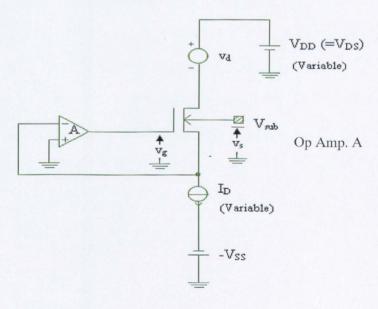

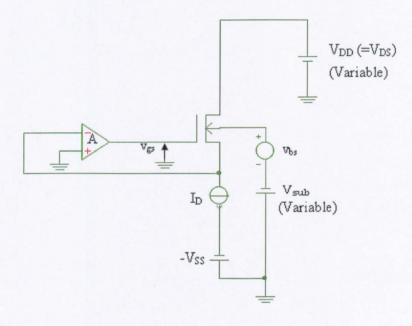

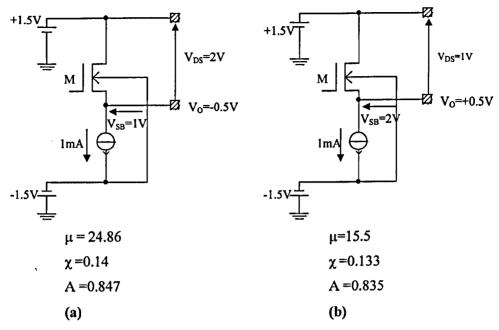

A test set-up for the measurement of  $\mu$  is shown in Fig.2.16: a similar set up, but with reversed DC biasing, applies to PMOS devices.

Figure 2.16 Test set-up for μ of an N channel MOSFET

In Fig.2.16, A is an op. amp. with a gain  $A_V$  (>>1) and a MOSFET input stage. Its purpose is to maintain constant, at earth potential, the source voltage of the MOSFET for different settings of  $I_{DS}$  and  $V_{DD}$  (= $V_{DS}$ ) and for any signal variations elsewhere in the circuit. Because the source is at earth the potential,  $V_{sub}$  applied to the substrate is a direct measure of the substrate-source voltage. Applying a small-signal (100mV peak) low-frequency (1KHz) sinusoidal signal,  $v_d$ , to the drain of the MOSFET does not causes a change in the source voltage or drain current because of the operation of A, which generates an opposing signal,  $v_g$ , at the gate terminal:  $v_d = v_{ds}$  and  $v_{gs} = v_g$ .

Thus,

$$i_d = g_m v_g + \frac{v_d}{r_{ds}} = 0$$

(2.8)

Hence,

$$v_g = -\frac{v_d}{g_m r_{ds}}$$

(2.9)

and,

$$\mu = \frac{g_m}{g_{ds}} = g_m r_{ds} = \left| \frac{-v_d}{v_g} \right|$$

(2.10)

This analysis assumes  $A_V = \infty$ . However, a full analysis in Appendix 2.2 shows that  $\mu$  is in error by not more than 0.1% if  $A_V > 10^3$  at the test frequency used.

Before simulation measurements were made, the circuit was checked for frequency stability and was found to be stable and it was also established that the op amp. gain exceeded 60dB [2.5] at the operating frequency chosen for tests.

In the tests it was noted that  $v_s$  was only a few  $\mu V$  for each reading, i.e., negligible in comparison with the observed  $v_g$ , thus validating the assumption that  $v_g = v_{gs}$ .

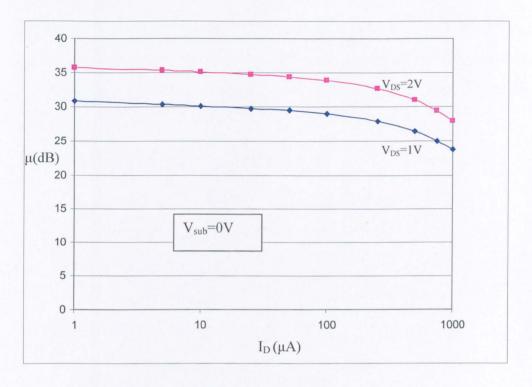

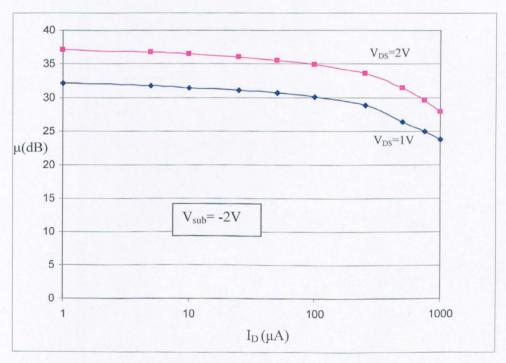

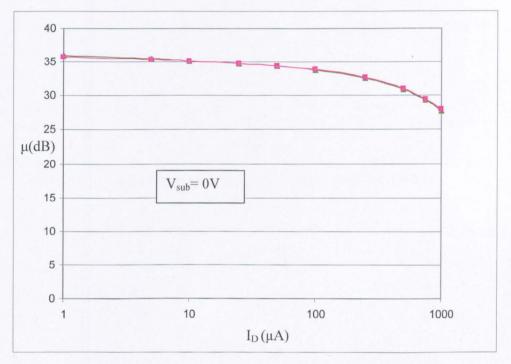

Tabulated data for  $\mu$  as a function of  $I_D$  for two values of  $V_{DS}$  (1V and 2V) and for two values of  $V_{sub}$  (0V and -2V) are given in Appendix2.3.

These data are presented graphically in Figs2.17, 2.18

Figure 2.17  $\mu$  as a function of  $I_D$  vs.  $V_{DS}$  with  $V_{sub}$ =0V

Figure 2.18  $\mu$  as a function of  $I_D$  vs.  $V_{DS}$  with  $V_{sub} = -2V$

It appears that the two curves for  $V_{DS}$  in Fig.2.17 differ by a constant amount throughout the range of  $I_D$  under test. To check to see of this was, in fact, the case one of the curves was displaced vertically to see if the two graphs could be made to coincide.

The result is displayed in Fig.2.19 for ease V<sub>sub</sub>=0V.

Figure 2.19 Showing the apparent coincidence of the two curves in Fig 2.17 when one of them is displaced vertically.

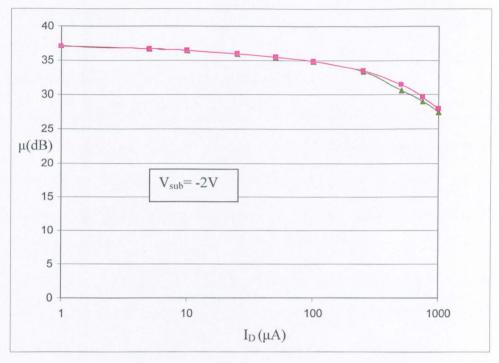

A similar displacement procedure was carried out for the plots of Fig.2.18: the result is shown in Fig.2.20

Figure 2.20 Showing the near coincidence of the curves in Fig.2.18

The general nature of the variation of  $\mu$  with  $I_D$  and  $V_{DS}$  in the strong inversion region of operation can be explored theoretically by replacing  $\lambda$  by (1 /  $V_A$ ) in eqn (2.1) and proceeding as follows

$$I_{D} = \frac{\beta}{2} (V_{GS} - V_{T})^{2} \cdot \left( 1 + \frac{V_{DS}}{V_{A}} \right)$$

(2.11)

By simple differentiation, and re-arrangement of terms,

$$r_{ds} = \frac{dV_{DS}}{dI_{DS}}\Big|_{V_{GS}} = \frac{V_A + V_{DS}}{I_D}$$

(2.12)

and,

$$g_{\rm m} = \frac{dI_{\rm DS}}{dV_{\rm DS}}\Big|_{V_{\rm DS}} = \sqrt{2I_{\rm D}\beta \frac{\left(V_{\rm A} + V_{\rm DS}\right)}{V_{\rm A}}}$$

(2.13)

Hence,

$$\mu = \sqrt{\frac{2\beta}{I_D V_A}} (V_A + V_{DS})^{\frac{3}{2}}$$

(2.14)

At low values of  $I_D$  the MOSFET enters the region of weak conversion where  $I_D$  is exponentially dependent on  $V_G$  [2.6].

In that case  $\mu$  takes on a constant maximum value.

Considering, now, Fig 2.17 it is apparent that, for both values of  $V_{DS}$ ,  $\mu$  is inversely related to  $I_D$  and tends toward a constant value at low currents. At higher currents, in the strong inversion region, eqn 2.13 predicts that  $\log \mu \propto \log I_D$  for a given  $V_{DS}$  (i.e.,  $\mu$ . in dB is linearly dependent on  $I_D$  plotted to a log scale) and this is not precisely true for the NMOS tested.

However, eqn (2.13) does predict a constant separation of the two curves in Fig 2.17 with variation in  $I_D$ . In assessing this it must be borne in mind that, for a given  $I_D$ ,  $V_{GS}$  decreases as  $V_{DS}$  increases and for each  $V_{GS}$  there is a different  $V_A$ .

Thus,

$$\mu_1 = \sqrt{\frac{2\beta}{I_D V_{A1}}} (V_{A1} + V_{DS1})^{\frac{3}{2}}$$

(2.15a)

and

$$\mu_2(>\mu_1) = \sqrt{\frac{2\beta}{I_D V_{A2}}} (V_{A2} + V_{DS2})^{\frac{3}{2}}$$

(2.15b)

Hence,

$$\left(\frac{\mu_2}{\mu_1}\right) = \sqrt{\frac{V_{A1}}{V_{A2}}} \left(\frac{V_{A2} + V_{DS2}}{V_{A1} + V_{DS1}}\right)^{3/2}$$

(2.16)

The maximum observed values of  $\mu$  for the NMOS is well over an order of magnitude lower than that of a BJT operating under the same DC bias conditions. For the BJT,  $\mu$ =(V<sub>A</sub>/V<sub>t</sub>) where V<sub>t</sub> = 'Thermal voltage' (KT/q)  $\approx$  25mV at room temp: for V<sub>A</sub> > 75V, and an operating current of 1mA  $\mu$   $\approx$  3000 for a BJT compared with  $\mu$  < 25 for the NMOS.

### 2.2.4(b) χ measurements

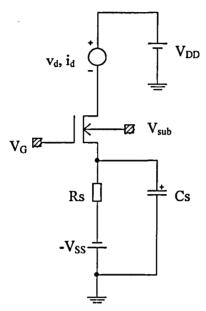

A variation of the set-up of Fig.2.16, shown in Fig.2.21, facilitates the measurement of  $(g_{mb}/g_m)$ . A similar set-up with reversed bias polarities applies to PMOS devices.

Figure 2.21 Set-up for finding (gmb/gm) for an NMOS

In this case a small amplitude (50mV) low frequency (1 KHz) sinusoidal signal,  $v_{bs}$ , is applied to the substrate in series with a variable (negative) substrate voltage  $V_{sub}$ . The amplifier A maintains the source of the MOSFET at earth potential and there is no change in drain current because the amplifier's output voltage  $v_{gs}$  nullifies any effect produced by  $v_{bs}$

$$i_{d} = 0 = g_{m} v_{gs} + g_{mb} v_{bs}$$

(2.17)

$$\therefore \quad \left| \frac{g_{mb}}{g_m} \right| = \left| \frac{v_{gs}}{v_{bs}} \right| \tag{2.18}$$

Tabulated data for  $\chi$  as a function of  $I_D$  for two values of  $V_{DS}$  (1V and 2V) and two values of  $V_{sub}$  (0V and 2V) are given in Appendix2.4

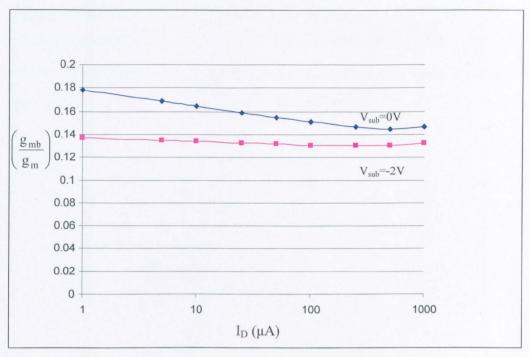

These data are presented graphically in Fig.2.22

Figure 2.22 Variation of  $(g_{mb}/g_m)$  with  $I_D$  for an NMOS MOSFET for  $V_{DS}\!\!=1V$  and two values of  $V_{sub}$

The variation of  $(g_{mb}/g_m)$  with  $V_{sub}$  is to be expected since, theoretically [2.7],

$$\left(\frac{g_{mb}}{g_m}\right) = \frac{\gamma}{2\sqrt{2\phi_F + V_{SB}}} \tag{2.19}$$

where the symbol have the meanings defined in Appendix2.1.

#### 2.2.4(c) Validation of parameter measurement techniques

To check the validity of the measurement techniques described in 2.2.4(a) for  $\mu$  and 2.2.4(b) for  $\chi(g_{mb}/g_m)$  an independent test was made, the circuit for which in shown in Fig.2.23.

Figure 2.23 Test circuit for output resistance measurement

The procedure was as follows. With  $V_{DD}=1V$ ,  $V_{SS}=2V$  and  $R_S=4K\Omega$  (arbitrary but convenient choices)  $V_G$  was adjusted at that, with  $V_{sub}=0V$ ,  $V_S=0V$ : hence,  $V_{DS}=V_{DD}$ , and  $I_D=0.5\text{mA}$ . The incremental output resistance  $v_{ds}(=v_d/i_d)$  was measured for the case of a decoupled source. This requires the use of a capacitor C (1F, totally impractical in a laboratory but acceptable in a simulation) having effectively zero reactance at the frequency of measurement, (1KHz).

The output resistance Ro was then found when C was absent.

The process was repeated for  $V_{sub}$ =-2V.

For calculation proposes [2.8],

$$R_{O} = R_{S} + r_{ds} [1 + (g_{m} + g_{mh})R_{S}]$$

(2.20)

Rearranging and substituting  $\mu$  for  $g_m r_{ds}$  gives,

$$R_{O} = r_{ds} + R_{S} \left[ 1 + \mu \left( 1 + \frac{g_{mb}}{g_{m}} \right) \right]$$

(2.21)

For the case  $V_{sub}$ =0V, Appendix 2.3 gives  $\mu$ =21.04 at  $I_D$ =0.5mA, and Appendix2.4 gives  $(g_{mb}/g_m)$ =0.1446

Substituting in eqn.2.21,

$$R_0(K\Omega)=3.67$$

(measured value) + 4 [1+ {(1.1446)×21.04}]

or,

$$R_O(K\Omega)=103.99$$

(calculated)

This compares with  $103.27K\Omega$  (simulation test).

For the case  $V_{sub}$ =-2V, Appendix2.3 gives  $\mu$ =23.2 at  $I_D$ =0.5mA and Appendix2.4 gives  $(g_{mb}/g_m)$ =0.13097

Substituting in eqn.2.21,

$$R_O(K\Omega)=4.05$$

(measured value) + 4 [1+ {(1.13097)× 23.2}]

or,  $R_O(K\Omega)=113$  (calculated)

This compares with 113.8K $\Omega$  (simulation result)

The excellent agreement between the two values of R<sub>O</sub> in each case validates the accuracy of the measurement techniques described in sections 2.2.4(a) and 2.2.4(b)

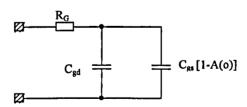

#### 2.2.5 Inter-electrode capacitor

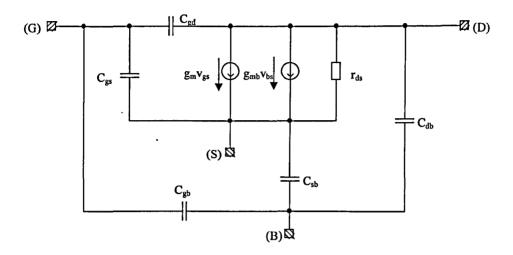

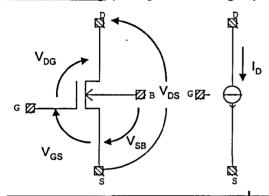

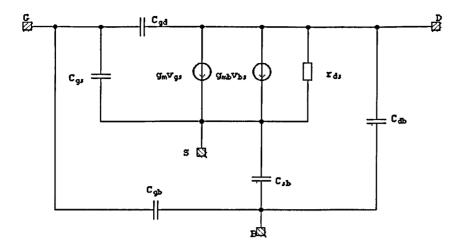

Fig.2.24 shows a small signal equivalent circuit of a NMOS transistor [2.8] presented in Appendix 2.1 and repeated here for convenience in the present discussion.

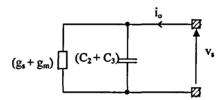

Figure 2.24 Small signal equivalent circuit of an NMOS transistor

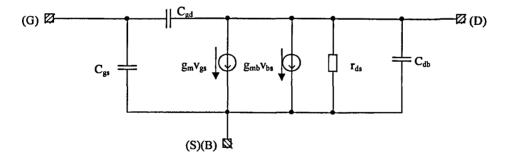

Fig.2.25 shows a simplified version, which applies when the substrate (B) is connected to the source terminal (S). As  $C_{gb}$  can not be separated from  $C_{gs}$  in normal MOSFET operation it is taken to be lumped in with  $C_{gs}$  in Fig.2.25 and henceforth.

Figure 2.25 Simplified version of Fig 2.24 when (S) and (B) are connected together.

The problem of measuring the three capacitances  $C_{gs}$ ,  $C_{gd}$  and  $C_{db}$  requires same ingenuity but can be solved by performing a sequence of tests that determines separately the following combinations:  $(C_{gs} + C_{gd})$ ;  $(C_{gd} + C_{db})$ ;  $(2C_{gs} + C_{gd} + C_{db})$ .

# 2.2.5(a) Test 1: Determination of (Cgs+Cgd)

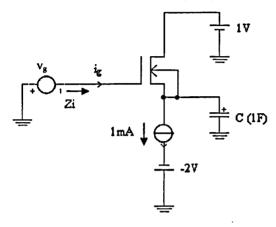

Figure 2.26 Test circuit for (Cgs+Cgd)

In the test circuit of Fig.2.26 a small amplitude (20mV) swept frequency sinusoidal test signal  $v_g$  applied to the gate of the test MOSFET produces a gate current  $i_g$ . The capacitor C (1F) is a source decupling capacitor. Cut frequencies for which its impedance is negligible we can write,

$$Zi = \frac{v_g}{i_g} = \frac{1}{j\omega(C_{gs} + C_{gd})}$$

(2.22)

On a plot of |Z|, to a dB scale with a reference value of  $1\Omega$ , against frequency on a log scale the point at which  $|Zi| = 1\Omega$  corresponds to  $f_0$ , say

Thus,

$$(C_{gs}+C_{gd}) = 1/2\pi f_0$$

(2.23)

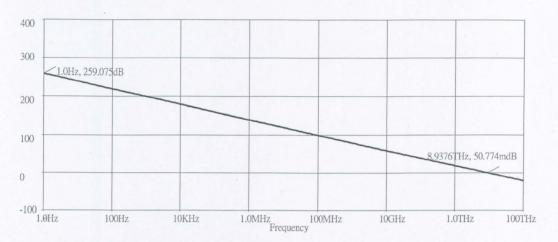

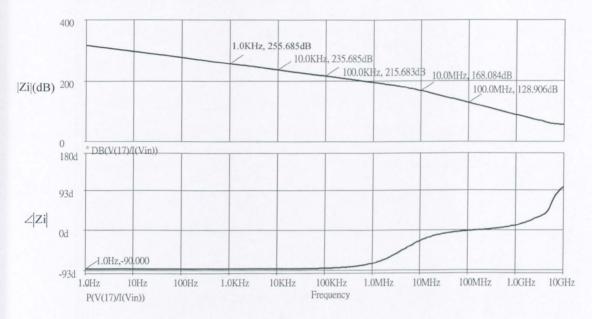

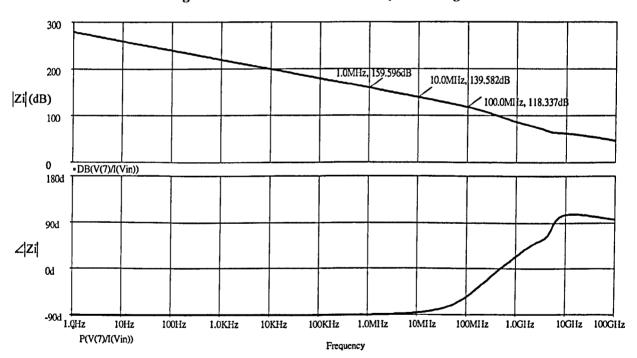

Figure 2.27 |Zi| vs. f for the circuit of Fig. 2.26

From Fig.2.26,  $|Zi| \approx 0$  dB (actually,  $50.77 \times 10\text{--}3$ ) at  $f_0 = 8.9376 THz$

Hence,  $(C_{gs}+C_{gd})\approx 17.8 fF$

# 2.2.5(b) Test 2: Determination of $(C_{gd}+C_{db})$

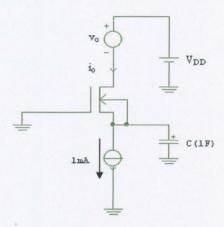

Fig.2.28 shows a test circuit for  $(C_{gd}+C_{db})$ , for which the test procedure mirrors that of the precious section.

Figure 2.28 Test circuit for (Cgd+Cdb)

By inspection the admittance at the drain of the MOSFET

is,

$$Y_o = \frac{i_o}{v_o} = g_{ds} + j\omega(C_{gs} + C_{db})$$

(2.24a)

or,

$$Z_{o} = \frac{1}{g_{ds} + j\omega(C_{gs} + C_{db})}$$

(2.24b)

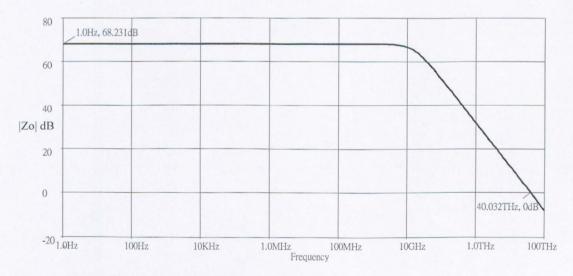

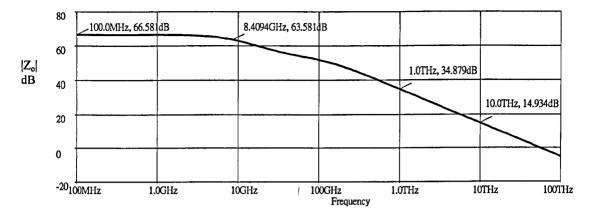

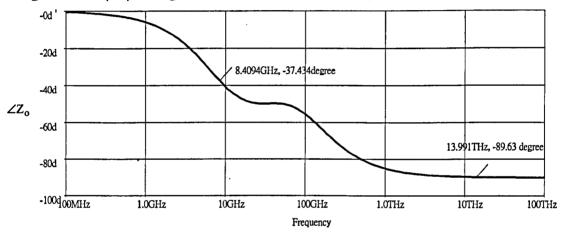

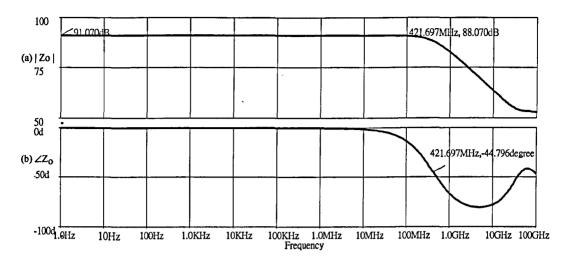

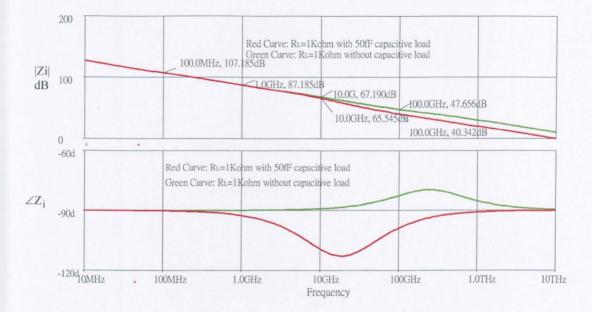

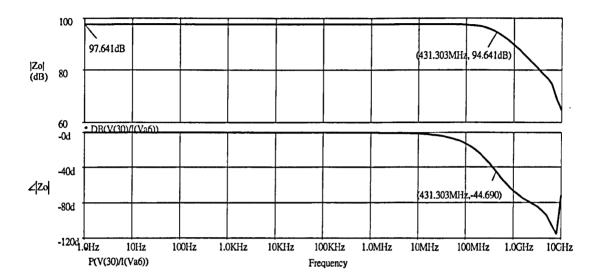

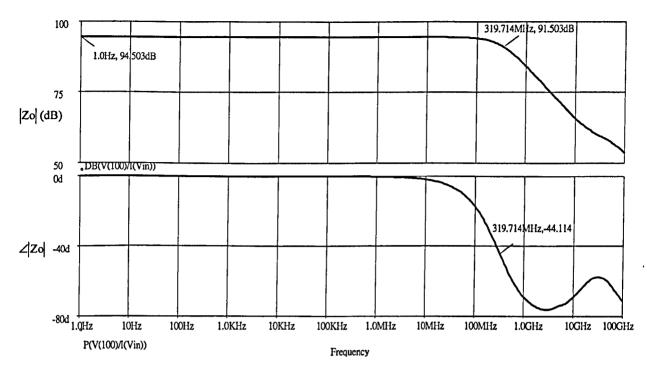

A plot of |Zo| vs. f is shown in Fig.2.29

Figure 2.29 |Zo| vs. f for circuit of Fig 2.28

Analysis and design of High-Transconductance RF MOSFET Voltage-to-Current Converters

The 'constant' value of |Zi| at low frequencies gives  $g_{ds} = 6.1677 \text{mS}$

Above  $f \approx 10 \text{GHz}$  the slope of the graph is -40dB / decade indicating a dominance of susuceptance over conductance in the expression for admittance.

For

$$f_o = 40.032$$

THz

$$|Z_{\rm o}| \approx 1\Omega$$

so,

$$(C_{gd} + C_{db}) = \frac{1}{2\pi \times 40.032 \times 10^{12}} F = 3.97 fF$$

# 2.2.5(c) Test 3: Determination of (2Cgs+Cgd+Cdb)

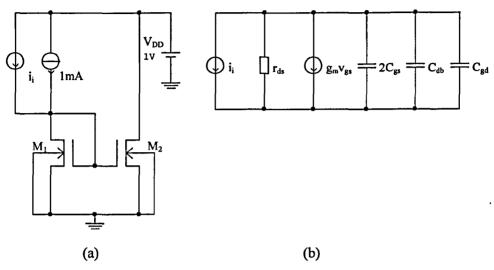

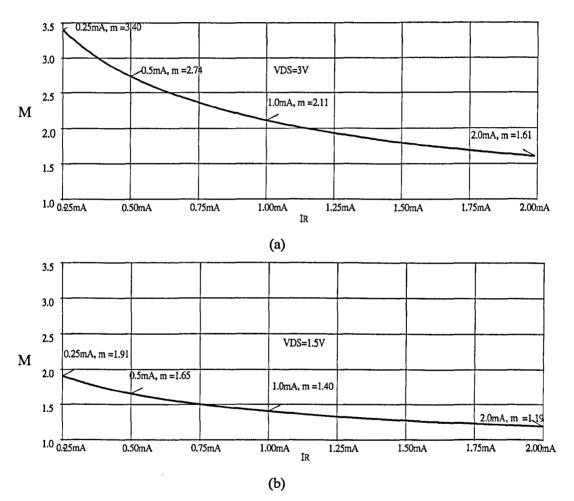

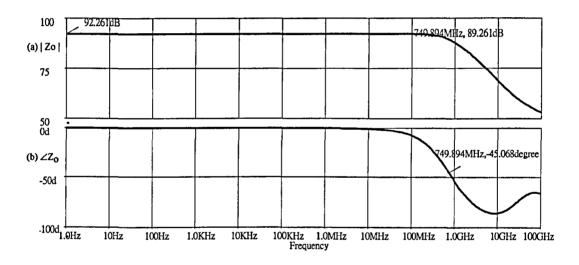

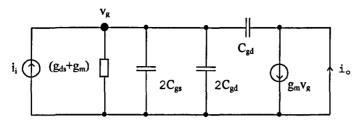

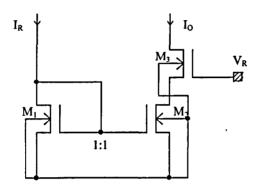

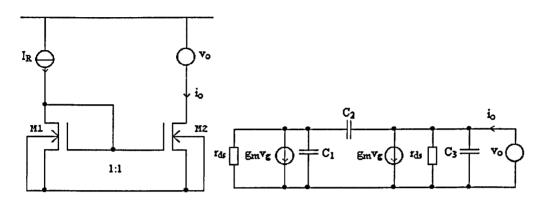

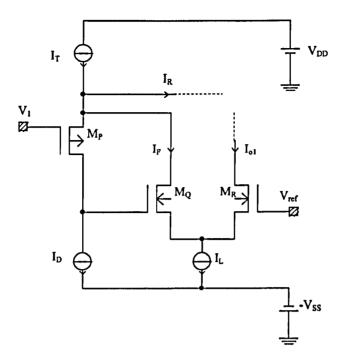

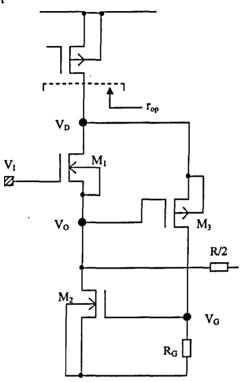

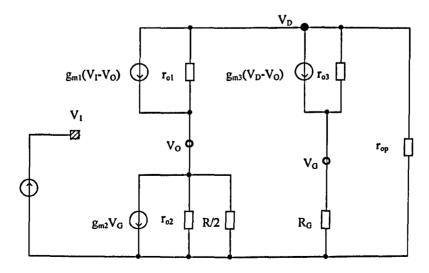

The test circuit for this is a simple 1:1 current mirror (Fig.2.30a) driven by a small swept frequency test current i<sub>i</sub>.

Figure 2.30 (a) Test circuit (b) Small signal equivalent circuit

In choosing this advantage was made of the fact that the gate-source capacitance,  $C_{gs}$ , is doubled but the  $C_{db}$  of  $M_2$  is not 'seen' by the input current. By inspection of Fig.2.31b,

$$Y_i = v_g [(g_{ds} + g_m) + j\omega(2C_{gs} + C_{db} + C_{gb})]$$

(2.25)

A plot of |Zi| vs. f, both on log values should give a -3dB point at,

$$f_o = \frac{(g_{ds} + g_m)}{2C_{gs} + C_{db} + C_{gb}}$$

(2.26)

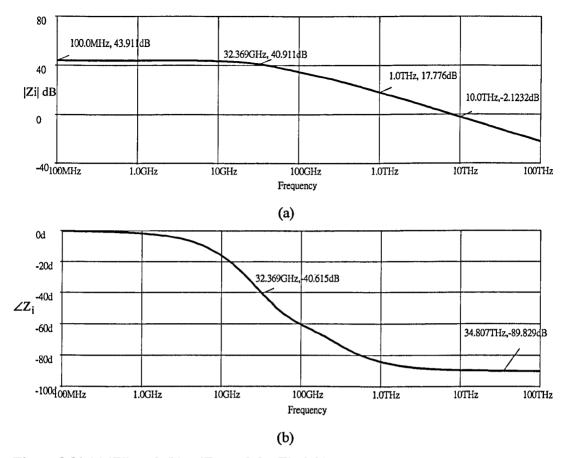

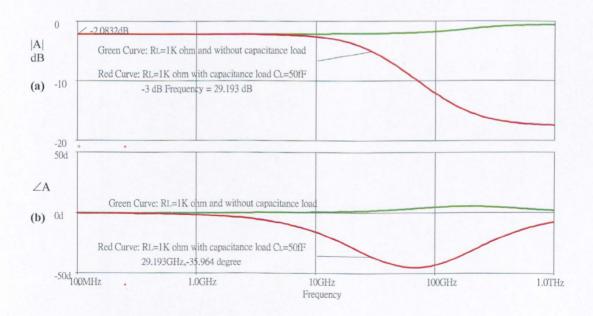

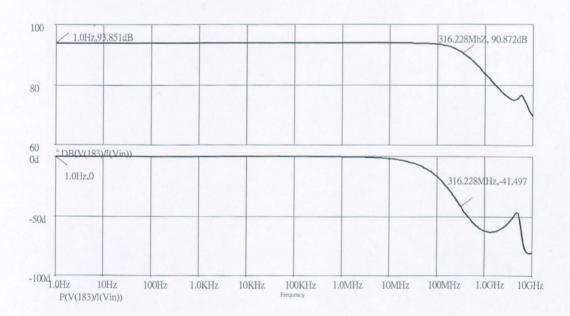

Figure 2.31 (a) |Zi| vs. f (b)  $\angle Z_i$  vs. f for Fig 2.30a

Fig.2.31a shows a plot of |Zi| vs. f and it appears that after an apparent -3dB at 32.369GHz the role off is -20dB. (The fall between 1THz and 10THz is actually 19.89dB)

However, the phase curve (Fig.2.31b) shows an inexplicable kink so the value of  $f_0$  must be regarded as approximate.

Using the data on Fig.2.31a,

$$2C_{gs}+C_{db}+C_{gd}=33fF$$

# 2.2.5(d) Calculations of $C_{gs}$ , $C_{gd}$ and $C_{db}$ from tests

We now have three equations and three unknowns.

Thus,

$$C_{gs}+C_{gd} = 17.8fF$$

$$C_{gd}+C_{db} = 3.97 fF$$

and,

$$2C_{gs}+C_{gd}+C_{db} = 33fF$$

Solving these eqns gives,

$$C_{gs}=14.5fF$$

;  $C_{gd}=3.33fF$ ;  $C_{db}=0.64fF$ .

In the case of the P channel MOSFET, the values obtained by simulation are follows:

$$C_{gs}+C_{gd} = 18.6fF$$

$$C_{gd} + C_{db} = 4.095 fF$$

$$2C_{gs} + C_{gd} + C_{db} = 34.09 fF$$

Solving above eqns. gives,

$$C_{gs}=15fF$$

;  $C_{gd}=3.6fF$ ;  $C_{db}=0.495fF$ .

#### 2.2 Summary

In this chapter the DC and some small-signal parameters of both N and P channel MOSFETs with channel length (L) of 0.13µm and channel width (W) of 10µm have been determined by simulation on test circuits and the results have been presented in tabular and/or graphical from.

Some interesting results were obtained. In particular; the threshold voltage,  $V_T$ , was found to be approximately linearly related to the source-substrate voltage,  $V_{SB}$ , rather than to the square root of  $V_{SB}$ , as stated in standard test books [2.10] (dealing with devices for which L > 1u); the DC output characteristics did not display a unique Early Voltage. A measurement technique thought to be novel for the direct determination of the dependence of the transconductance ratios  $(g_m/g_{ds})$  and  $(g_{mb}/g_m)$  was proposed. Finally, tests we made to find the values of the inter-electrode capacitances  $C_{gs}$ ,  $C_{gd}$ ,  $C_{db}$ . The value of  $C_{gd}$  was not insignificant, and might be expected from the textbook discussion on 'long channel devices' (L >> 1um)

\*This conclusion was subsequently confirmed by a note in a book. (Fundamentals of High Frequency CMOS Analog Design, D. Leblibici and Y. Leblibici, Cambridge University Press, 2009, pp.24). However, no explanation is given for the phenomenon.

#### 2.3 References

- [2.1] Allen P. E. and Holberg D. R., 'CMOS Analog Circuit Design', Oxford University Press, Second Edition, New York, 2002, pp. 76

- [2.2] Allen P. E. and Holberg D. R., 'CMOS Analog Circuit Design', Oxford University Press, Second Edition, New York, 2002, pp. 40

- [2.3] Gray P. R., Hurst P. J., Lewis S. H. and Meyer R. G., 'Analysis and Design of Analog Integrated Circuits', John Wiley & Sons, Inc., Fourth Edition, New York, 2001, pp. 43-44

- [2.4] Gray P. R., Hurst P. J., Lewis S. H. and Meyer R. G., 'Analysis and Design of Analog Integrated Circuits', John Wiley & Sons, Inc., Fourth Edition, New York, 2001, pp. 53

- [2.5] National Semiconductor, 'LMC660 CMOS Quad Operational Amplifier General Description', Datasheet, 2006

- [2.6] Smith S., 'Microelectronic Circuits', Oxford University Press, Third Edition, New York, 1991, pp. 308-311

- [2.7] Gray P. R., Hurst P. J., Lewis S. H. and Meyer R. G., 'Analysis and Design of Analog Integrated Circuits', John Wiley & Sons, Inc., Fourth Edition, New York, 2001, pp. 54

- [2.8] Gray P. R., Hurst P. J., Lewis S. H. and Meyer R. G., 'Analysis and Design of Analog Integrated Circuits', John Wiley & Sons, Inc., Fourth Edition, New York, 2001, pp. 55

- [2.9] Gray P. R., Hurst P. J., Lewis S. H. and Meyer R. G., 'Analysis and Design of

- Analog Integrated Circuits', John Wiley & Sons, Inc., Fourth Edition, New York, 2001, pp. 195-197

- [2.10] Allen P. E. and Holberg D. R., 'CMOS Analog Circuit Design', Oxford University Press, Second Edition, New York, 2002, pp. 73-79

- [2.11] Gray P. R., Hurst P. J., Lewis S. H. and Meyer R. G., 'Analysis and Design of Analog Integrated Circuits', John Wiley & Sons, Inc., Fourth Edition, New York, 2001, pp. 74

# 2.4 Appendix 2

# Appendix 2.1 MOSFET Symbol definition and parameter relationships. (Based on [2.11])

DC Relationship (Strong inversion region)

Saturated region (Current saturation)

$V_{GS} > 0$  and  $V_{GD} < V_T (V_{DG} > V_T)$

$$I_D(=I_{DS}) = \frac{\mu_n C_{ox}}{2} \frac{W}{L} (V_{GS} - V_T)^2 (1 + \lambda V_{DS})$$

or,

$$I_D = \frac{\beta}{2} (V_{GS} - V_T)^2 (1 + \lambda V_{DS})$$

where  $\beta = (\mu_n C_{ox} W/L)$

W= gate width; L= gate length

'Triode region' (Voltage Saturation)

$$V_{DS} < (V_{GS} - V_T)$$

or  $V_{GD} > V_T$

$$I_{D}(=I_{DS}) = \frac{\mu_{n}C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{T})^{2} (1 + \lambda V_{DS})$$

$$I_{D}(=I_{DS}) = \frac{\mu_{n}C_{ox}}{2} \frac{W}{L} [2(V_{GS} - V_{T})V_{DS} - V_{DS}^{2}]$$

or,

$$I_{D} = \frac{\beta}{2} (V_{GS} - V_{T})^{2} (1 + \lambda V_{DS})$$

or,

$$I_{D} = \frac{\beta}{2} [(V_{GS} - V_{T})^{2} (V_{GD} - V_{T})^{2}]$$

where

$$\beta = (\mu_{D}C_{ox}W/L)$$

or,

$$I_D = \frac{\beta}{2} [(V_{GS} - V_T)^2 (V_{GD} - V_T)^2]$$

Threshold voltage:

$$V_T = V_{T0} + \gamma \sqrt{2\phi_f + V_{SR}} - \sqrt{2\phi_f}$$

Threshold voltage parameter:  $\gamma = \frac{1}{C_{out}} \sqrt{2q\epsilon N_A}$

Oxide capacitance:

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} = 3.45 \text{ fF/um}^2 \text{ for } t_{ox} = 100 \text{ Å}$$

Small-signal relationships

Small-Signal Operation (Active Region) Parameters

Top-gate transconductance:

$$\left(\frac{\partial I_{D}}{\partial V_{GS}}\right) = g_{m} = \mu_{n} C_{ox} \frac{W}{L} (V_{GS} - V_{T})(1 + \lambda V_{DS}) = \sqrt{2I_{D}\mu_{n} C_{ox} \frac{W}{L}} (1 + \lambda V_{DS}) = \sqrt{2I_{D}\beta} (1 + \lambda V_{DS})$$

Transconductance-to-current ratio:

$$\frac{g_m}{I_D} = \frac{2}{V_{GS} - V_T}$$

Body-effect transconductance:

$$g_{mb} = \frac{\gamma}{2\sqrt{2\phi_f + V_{SB}}} g_m = \chi g_m \left( = \frac{\partial I_D}{\partial V_{BS}} \right)_{V_{CS} = constant}$$

Channel-length modulation parameter:

$$\lambda = \frac{1}{V_A} = \frac{1}{L_{eff}} \frac{dX_d}{dV_{DS}}$$

where  $X_d$  is the depletion-layer width.

Output resistance:

$$r_{ds} = \frac{\left(1 + \lambda V_{DS}\right)}{\lambda I_{D}} = \frac{L_{eff}}{I_{D}} \left(\frac{dX_{d}}{dV_{DS}}\right)^{-1}$$

Effective channel length:

$$L_{eff} = L_{drwn} - 2L_d - X_d$$

Maximum gain:

$$\mu \underline{\Delta} g_{m} r_{ds} = \frac{1}{\lambda} \frac{2}{V_{GS} - V_{T}} = \frac{2V_{A}}{V_{GS} - V_{T}}$$

Source-body depletion capacitance:

Analysis and design of High-Transconductance RF MOSFET Voltage-to-Current Converters

$$C_{sb} = \frac{C_{sb0}}{\left(1 + \frac{V_{SB}}{\psi_0}\right)^{0.5}}$$

Drain-body depletion capacitance:

$$C_{db} = \frac{C_{db0}}{\left(1 + \frac{V_{DB}}{\psi_0}\right)^{0.5}}$$

Gate-source capacitance:

$$C_{gs} = \frac{2}{3} WLC_{ox}$$

Transition frequency:

$$f_{T} = \frac{g_{m}}{2\pi \left(C_{gs} + C_{gd} + C_{gb}\right)}$$

# Appendix 2.2 Analysis of the µ measurement circuit

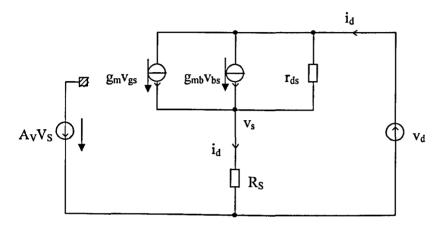

Fig.A2.2 shows a small signal low-frequency equivalent circuit of Fig.2.21 in the text and the condition that exist when a signal,  $v_d$ , is applied to the drain of the MOSFET. The op-amp. voltage gain,  $A_V$ , and incremental output resistance,  $R_S$ , of the current sink,  $I_{DS}$ , are considered to be finite.

Figure A2.2 Small signal equivalent circuit for Fig 2.21 of the text

$$g_{m}v_{gs} = g_{m}(v_{g} - v_{s}) = g_{m}(-Av_{s} - v_{s}) = -(A_{V} + 1)g_{m}v_{s}$$

$$g_{mb}v_{bs} = g_{mb}(v_{b} - v_{s}) = -g_{mb}v_{s} \text{ (since } v_{b} = 0v\text{)}.$$

KCL at the drain gives,

$$i_d = g_m v_{gs} + g_{mb} v_{bs} + (v_d - v_s)/r_{ds}$$

Substituting for  $v_{gs}$  and  $v_{bs}$ ,

$$i_d = -(A_V + 1)g_m v_s - g_{mb} v_s + (v_d - v_s)/r_{ds}$$

KCL at the source gives,

$$\therefore \frac{v_s}{R_s} = -[(A_V + 1)g_m + g_{mb}]v_s + \frac{v_d - v_s}{r_{ds}}$$

Transposing,

$$v_s = \left[\frac{1}{R_S} + (A_V + 1)g_m + g_{mb} + \frac{1}{r_{ds}}\right] = \frac{v_d}{r_{ds}}$$

or,

$$\frac{v_s}{v_d} = \frac{1}{r_{ds} \left[ \frac{1}{R_s} + (A_v + 1)g_m + g_{mb} + \frac{1}{r_{ds}} \right]}$$

Analysis and design of High-Transconductance RF MOSFET Voltage-to-Current Converters

$$\frac{v_s}{v_d} = \frac{1}{\left(\frac{r_{ds}}{R_s} + 1\right) + r_{ds}\left[\left(A_V + 1\right)g_m + g_{mb}\right]}$$

$$\cdot \text{ But, } v_g = -A_V v_s$$

$$\therefore v_g = \frac{-A_V v_d}{\left(\frac{r_{ds}}{R_s} + 1\right) + r_{ds}\left[\left(A_V + 1\right)g_m + g_{mb}\right]}$$

For  $R_S >> r_{ds}$ , the first bracketed term is the denominator is insignificant compared with the second bracketed term so this reduces to,

$$v_{g} = \frac{-A_{V}v_{d}}{(A_{V} + 1)g_{m}r_{ds} + g_{mb}r_{ds}}$$

or,

$$\frac{v_{d}}{v_{g}} = -\frac{(A_{V} + 1)g_{m}r_{ds} + g_{mb}r_{ds}}{A_{V}}$$

$$\therefore \qquad \left|\frac{v_{d}}{v_{g}}\right| = \left(1 + \frac{1}{A_{V}}\right)\mu + \left(\frac{g_{mb}}{g_{m}}\right)\frac{\mu}{A_{V}}$$

But

$$(g_{mb}/g_{m}) < 1$$

$$\left|\frac{v_{d}}{v_{s}}\right| < \left(1 + \frac{2}{A_{V}}\right)\mu$$

For  $A_V > 2000$ ,  $\left| \frac{v_d}{v_s} \right|$  gives  $\mu$  with an accuracy better than 0.1 %

# Appendix 2.3

Listed below in Table.2.1 are data for  $\mu$  as a function of  $I_D$  for two values of  $V_{DS}$  (1V and 2V), for  $V_{sub}$ =0V

Table A2.1  $\mu = f(I_D, V_{DS})$

| I- ( A) | N/00   |       | u dD  |

|---------|--------|-------|-------|

| ID(μA)  | VDS(V) | μ     | µ dB  |

| 1       | 1      | 34.82 | 30.84 |

|         | 2      | 61.34 | 35.75 |

| 5       | 1      | 33.2  | 30.42 |

|         | 2      | 58.88 | 35.4  |

| 10      | · 1    | 32.9  | 30.18 |

|         | 2      | 57.35 | 35.17 |

| 25      | 1      | 30.96 | 29.81 |

|         | 2      | 54.84 | 34.78 |

| 50      | 11     | 29.81 | 29.49 |

|         | 2      | 52.54 | 34.41 |

| 100     | 1      | 28.83 | 29.04 |

|         | 2      | 49.58 | 33.91 |

| 250     | 1      | 25    | 27.96 |

|         | 2      | 43.35 | 32.74 |

| 500     | 1      | 21.04 | 26.46 |

|         | 2      | 35.6  | 31    |

| 750     | 1      | 18    | 25.11 |

|         | 2      | 29.64 | 29.44 |

| 1000    | 1      | 15.5  | 23.8  |

|         | 2      | 24.86 | 27.91 |

# Appendix 2.4 Tabular data on (gmb/gm)

Table A2.2

|        | (gmb/gm) | (gmb/gm)  |

|--------|----------|-----------|

| Ισ(μΑ) | Vsub=0V  | Vsub= -2V |

| 1      | 0.178    | 0.137     |

| 5      | 0.169    | 0.135     |

| 10     | 0.165    | 0.134     |

| 25     | 0.159    | 0.133     |

| 50     | 0.155    | 0.132     |

| 100    | 0.151    | 0.131     |

| 250    | 0.147    | 0.131     |

| 500    | 0.145    | 0.131     |

| 1000   | 0.147    | 0.133     |

# **CHAPTER 3**

# DESIGN CONSIDERATIONS FOR BASIC SUB-CIRCUITS

- 3.1 Introduction

- 3.1(a) The simple current mirror (CM)

- 3.1(b) The Widlar CM

- 3.2 Multi-transistor CMs

- 3.2.1 DC Characteristics

- 3.2.2 Incremental performance

- 3.3 The Source-Follower

- 3.3.1 DC Characteristics

- 3.3.2 Incremental performance

- 3.4 Summary and Conclusions

- 3.5 References

- 3.6 Appendix 3

- Appendix 3.1 Output impedance of a 1:1 CM

- Appendix 3.2 Source-Follower analysis

- Appendix 3.3 Additional Source-Follower characteristics

#### 3.1 Introduction

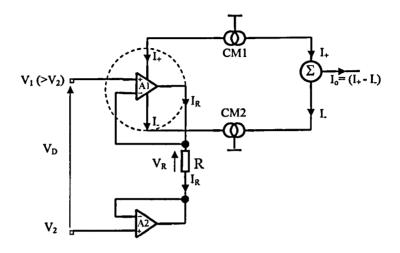

The current mirror, in its basic form or in a variant of it, together with the source-follower are basic sub-circuits in CMOS analogue design. A glance at the literature shows that they certainly feature widely in existing V-I designs.

Conventional textbook treatments deal with the analysis of both types of circuit using MOSFETs with channel lengths greater than about 1 µm.

This chapter includes simulated measurements made to assess, for future use and reference, the performance of a number of types of current mirror and the performance of the source-follower incorporating MOSFETs with a channel length of  $0.13 \ \mu m$ .

# 3.1(a) The simple current mirror (CM)

The simple of 1:1 current mirror, comprising two MOSFETs with

Figure 3.1 Simple (1:1) Current Mirror

identical characteristics, driven by an input reference current  $I_R$  (See Fig.3.1) has been touched-on in Chapter 2 in the discussion on MOSFET output characteristics (See Section2.2.3) where it was established that incremental output resistance in the

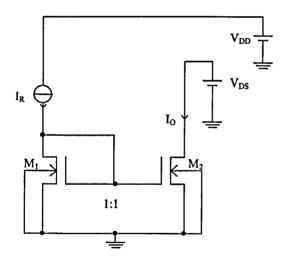

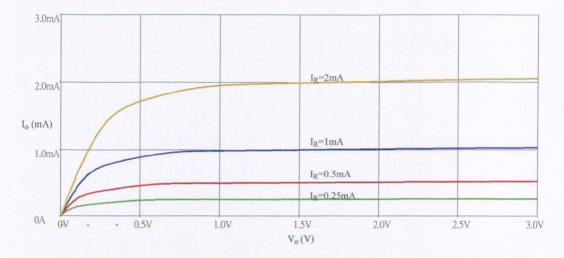

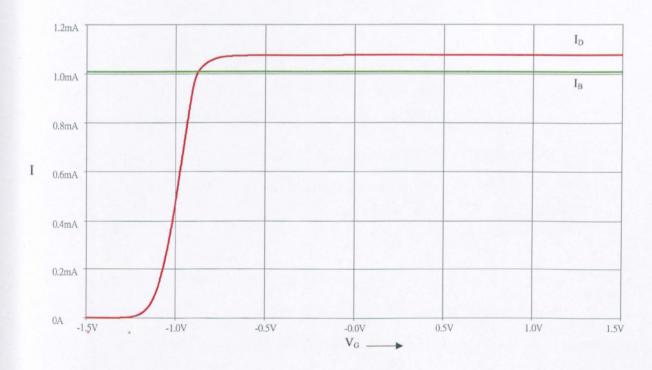

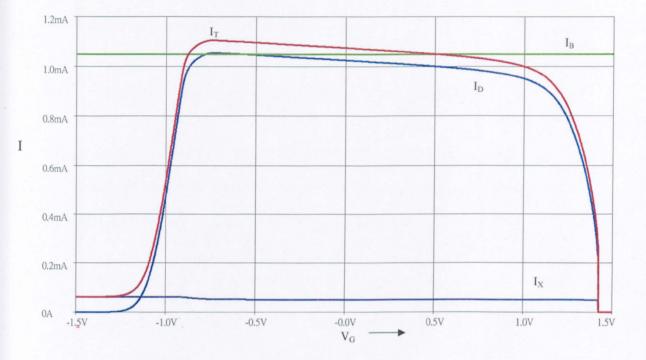

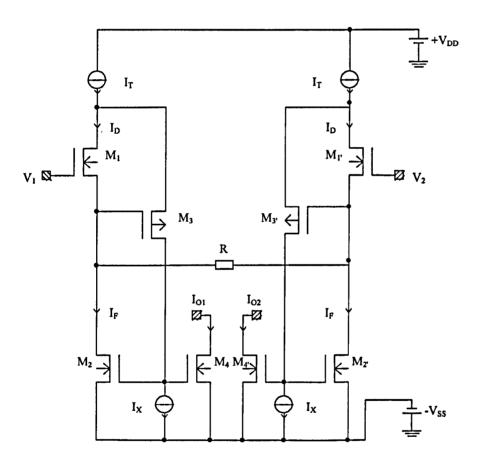

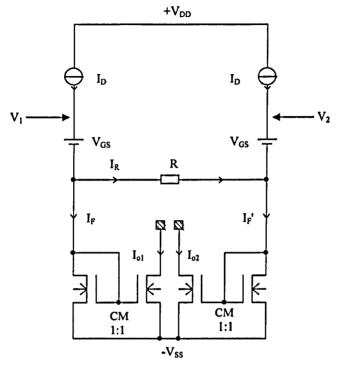

'current saturation' region, for the devices under test, was small,  $2K\Omega$  (approx.) for  $I_R=1$ mA. This makes the CM of extremely limited use if the output circuit of  $M_2$  is to approximate a good, predicable current sink. The poor performance of the circuit of Fig.3.1 is clearly evident from Fig.3.2 which shows the DC current transfer ratio  $M(=I_O/I_R)$  as a function of  $I_R$  for two values of  $V_{DS}$ .

Figure 3.2 DC current transfer ratio M for Fig 3.1, as a function of  $I_R$  and  $V_{DS}$ (a) for  $V_{DS}$ =3V; (b)  $V_{DS}$ =1.5V

For a 1: x (>1) CM, in which L is the same for  $M_1$  and  $M_2$  but W for  $M_2$  is a factor x greater than that of  $M_1$ , additional measurements (not included here) for x = 2 show, as expected, that for a given  $I_R$  and  $V_{DS}$ ,  $I_D$  and  $g_{ds}$  are both double the Figure for x=1.

The DC performance the PMOS 1:1 CM using MOSFETs with L=0.13 $\mu$ m and W=10 $\mu$ m is better because of the higher output resistance obtainable with these devices.

It has been assumed above that the characteristics of  $M_1$  and  $M_2$  are identical. Simulations of current mirrors automatically assume this unless provisions are made for them to be different.

In practice, of course, doping and lithographic variations mean that even with the same  $V_{DS}$  [3.1].

$$M = \frac{I_O}{I_R} = 1 \pm \frac{\Delta \beta}{\beta} \pm \frac{2\Delta V_T}{(V_{GS} - V_T)}$$

(3.1)

where  $\Delta\beta/\beta$  is the fractional variation in  $\beta$  and  $\Delta V_T$  is the Threshold Voltage difference. Eqn.3.1 suggests closer matching for higher  $V_{GS}$ , i.e. higher  $I_D$ .

By simple inspection the input impedance of a 1:1 CM is,

$$Z_{i} = \frac{1}{(g_{ds} + g_{m}) + (2C_{es} + C_{ds} + C_{ed})s}$$

(3.2)

Fig.2.2.5(c) in the previous Chapter shows  $|Z_i|$  vs. f for  $I_D = 1$  mA and  $V_{DS} = 1$  V

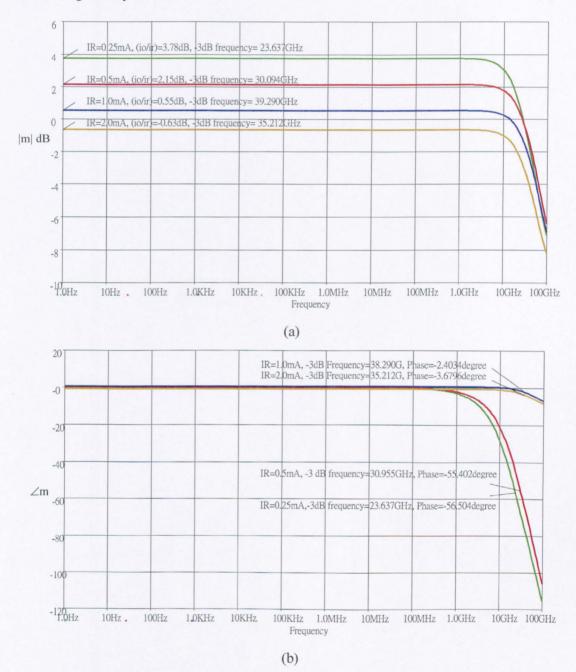

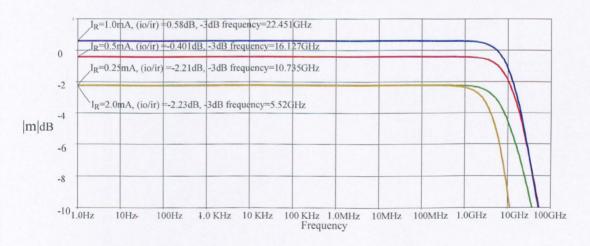

A straightforward small signal analysis shows that the current gain m (j $\omega$ ) = (i $_{o}$ /i $_{r}$ ) has a pole at,

$$\omega_{p} = \frac{(g_{m} + g_{ds})}{(2C_{gs} + C_{db} + C_{gd})}$$

(3.3)

There is also a zero at,

$$\omega_z = \frac{g_m}{C_{gd}} \tag{3.4}$$

This zero is not mentioned in [3.1], presumably because  $\omega_z \gg \omega_p$

A plot of m(jω) for the circuit of Fig.3.1 is given in Fig.3.3

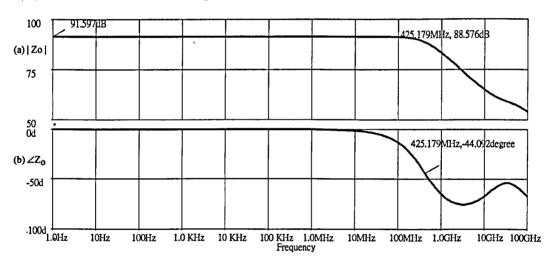

Surprisingly, the output impedance (as compared with the output resistance) is not treated in generally available textbooks. A full treatment is given in Appendix3.1

where it is shown that the expression for  $Z_o$  contains a zero in addition to two poles. Representing the output by the parallel combination of a resistor and a capacitor is, thus, not generally valid.

Figure 3.3 Current transfer ratio 'm' as a function of frequency for Fig 3.1.  $V_{DS}$ =1.5V. (a) Magnitude (b) Phase

Figure 3.4 |Zo| for Fig 3.1. Reference resistance =  $1\Omega$ , here and elsewhere

Figure 3.5  $\angle Z_0$  for Fig 3.1

Figs 3.4, 3.5 respectively show  $|Z_0|$  vs. f and  $\angle Z_0$  vs. f.

From the analysis, a predicted value for -3dB frequency is 7.6GHz.

In Fig.3.4 the -3dB point for  $|Z_0|$  is at the higher value of 8.4 GHz. The difference can be accounted for by a zero at a lower frequency.

This shows itself more clearly in the flattened phase characteristic (Fig.3.5) between 10GHz and 100GHz. This causes a fall-off in  $|Z_0|$  by less than 20dB/decade and results in a higher -3dB point for  $|Z_0|$ . The final fall-off rate of 20dB/decade is as predicted.

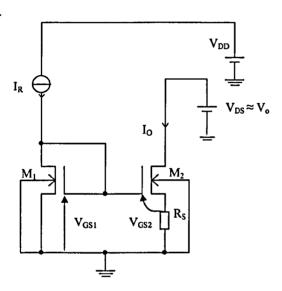

#### 3.1(b) The Widlar CM

The purpose of the Widlar CM, shown in Fig.3.6, in which  $M_1$  and  $M_2$  are assumed to have identical characteristics, is to produce an output current Io that is a fraction, usually small, of the input current  $I_R$ . This is set by choice of the source degeneration resistor  $R_S$ .

Figure 3.6 The Widlar CM

Assuming a simple square-law relationship between  $I_D$  and  $V_{GS}$ , and ignoring differences in  $V_{DS}$  between  $M_1$  and  $M_2$  and threshold voltage differences.

$$V_{GS1} = \sqrt{\frac{2\beta}{I_R}} + V_T \tag{3.5}$$

and,

$$V_{GS2} = \sqrt{\frac{2\beta}{I_O}} + V_T$$

(3.6)

Hence,

$$R_S = \frac{(V_{GS1} - V_{GS2})}{I_O} = \frac{\sqrt{2\beta}}{I_O} \left[ \frac{1}{\sqrt{I_R}} - \frac{1}{\sqrt{I_O}} \right]$$

(3.7)

Given  $I_0$ ,  $R_s$  can be chosen for a given  $I_R$  and known  $\beta$ .

The  $V_{SB}$  of  $M_2$  can be allowed for, in an iterative design process, as can the non-identical  $V_{DS}$  of  $M_1$  and  $M_2$ .

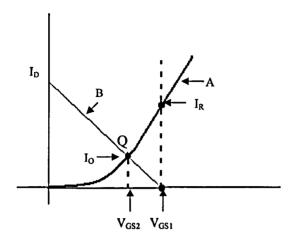

However, the graphical approach proposed here and shown in Fig.3.7 is simpler in practice.

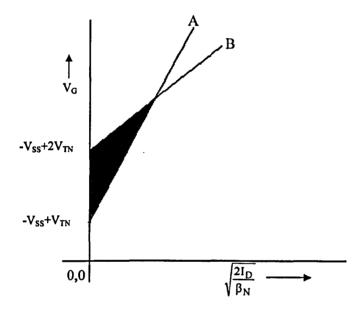

Figure 3.7 Graphical construction to find R<sub>S</sub> for a specified I<sub>0</sub>

Curve 'A' represents the  $I_D$  vs.  $V_{GS}$  characteristic for both  $M_1$  and  $M_2$ .  $V_{GS1}$  and  $V_{GS2}$  correspond, respectively, to  $I_D = I_R$  and  $I_D = I_O$  (at the point Q). Line B, passing through Q, has a slope -1/R<sub>S</sub>: hence, R<sub>S</sub> can be determined.

Using this approach  $R_S$  was found to be  $4K\Omega$  for a specified value of  $I_O$  of  $50\mu A$  (approx.) with  $I_R$  =1mA and  $V_{DS}$  = 1.0 V. The simulated value of  $51.34\mu A$  is slightly higher than the specified value because of the  $V_{DS}$  of  $M_2$  exceeds that of  $M_1$ . (i.e.,  $V_O > V_{CS}$ ).

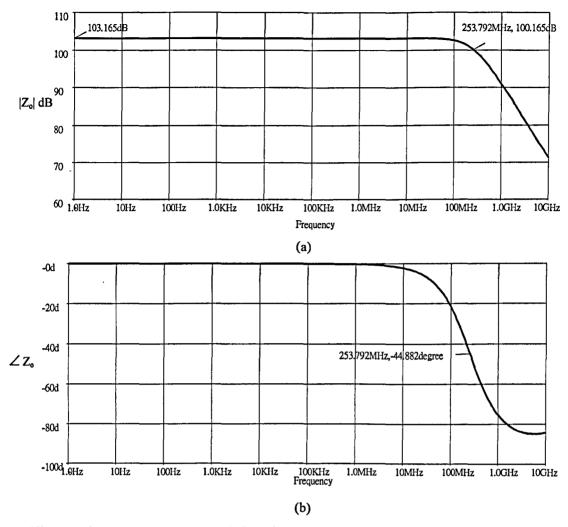

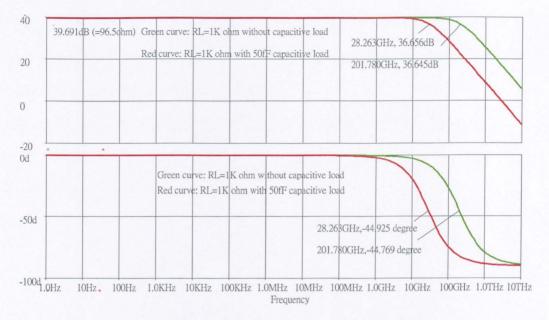

Figure 3.8 Output characteristics of the Widlar CM: (a)  $|Z_0|$  (b)  $\angle Z_0$

Fig 3.8 shows variation of output impedance,  $Z_0$ , with frequency. Over its 'constant' region  $|Z_0| = R_0 = 103.165 dB$  (for a dB reference value of  $1\Omega$ ), corresponding to an incremental output resistance of  $144 K\Omega$ .

As in the case of a simple CM, a general expression for  $Z_0$ , in terms of the frequency variable s, in complex.

However, because of the large Ohmic value of  $R_0$ , there is a dominant pole at the output, for it is an apparent that the roll-off occurs at a rate of -20dB/decade (approx.) up to 10GHz.

The -3dB cut off frequency  $(1/2\pi R_o C_o)$  is 273.5 MHz, indicating an output capacitance of 4fF that corresponds precisely with the already determined 4fF output capacitance of  $M_2$ .

The current fed back via  $C_{gd}$  from the drain of  $M_2$  to its gate is not mirrored by  $M_2$  because of the presence of  $R_S$  in its source lead.

# 3.2 Multiple transistor CMs

The observed limitations of the simple CM, using MOSFETs with channel lengths of 0.13µm, with respect to source/sink/repeater operation make it necessary to employ multiple transistor CMs for predictability in DC current transfer ratio, M, and increased incremental output resistance.

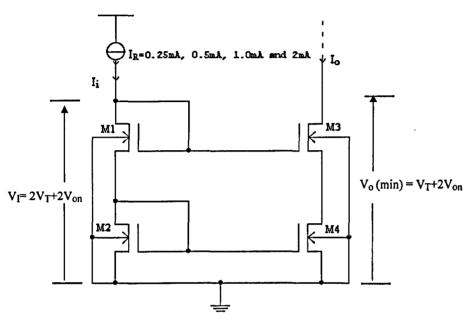

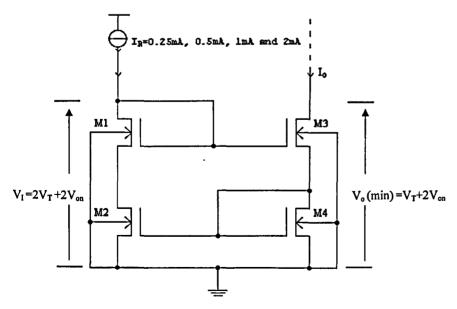

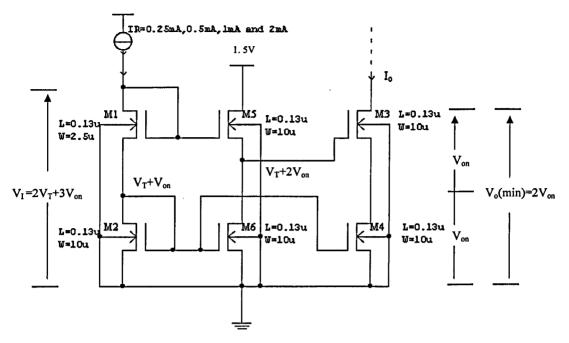

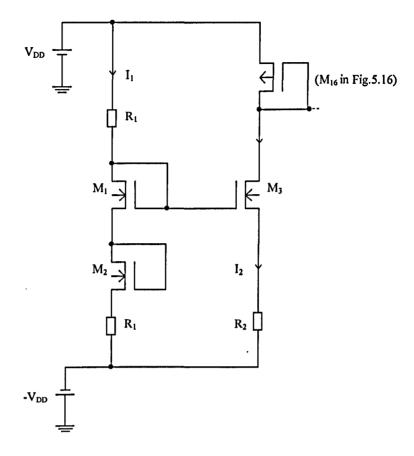

Those popular choices are: the Cascode CM (CCM), Fig.3.9; the Modified Wilson CM (MWCM), Fig.3.10; and the so-called High Output Compliance CM (HCCM), Fig.3.11.

#### 3.2.1 DC Characteristics

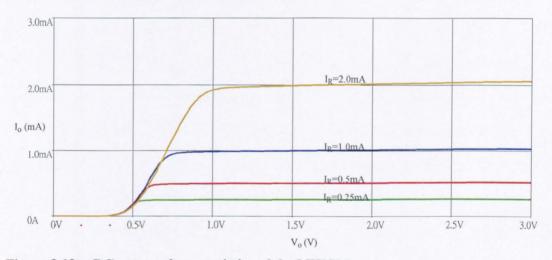

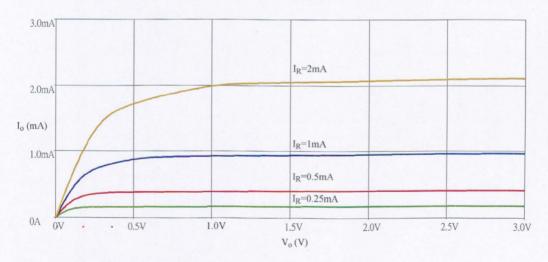

The DC and incremental performance of these are compared in this section, with a view to their application in V-I design, starting with the DC characteristics in Figs3.12, 3.13, 3.14.

For the CCM and MWCM the gate of  $M_3$  is held at  $(V_{T4}+V_{T3}+2V_{on})$ ,

where  $V_{on} = (V_{GS} - V_T) = \sqrt{2I_R/\beta}$  and is the minimum  $V_{DS}$  for operation in the current saturation region. Hence  $V_o(min) = V_{T4} + V_{T3} + 2V_{on} - V_{T3} = V_T + 2V_{on}$ . The interesting conclusion is that  $V_o(min)$  is the same as it would be if the substrate of  $M_1$ ,  $M_3$  were connected to their respective sources. In the case of the WCM,  $I_O=0$  for  $V_I < (V_{T3}+V_T)$ .

The HCCM uses six MOSFETs to obtain the theoretical value  $V_o(min)\approx 2V_{on}$ . Working back from the gate of  $M_3$ , the nodal voltage labelling shows that that this is achievable if all the MOSFETs expect  $M_1$  have identical characteristic with a common beta parameter ' $\beta$ ' and common threshold voltage,  $V_T$ .

Figure 3.9 The Cascode CM (CCM): Von is defined on p 3.10

Figure 3.10 The Modified Wilson CM (MWCM)

Figure 3.11 'High Output Compliance' CM (HCCM): Theoretical Design

$M_1$  must have the same  $V_T$  as all the other MOSFETs but a beta parameter  $\beta_4$ :  $\beta_4 \neq \beta$  because we require the  $V_{on}$  of  $M_1$  to be twice the common value of the other devices.

Thus,

$$\sqrt{\frac{2I_R}{\beta_4}} = 2\sqrt{\frac{2I_R}{\beta}}$$

(3.8)

Hence,  $\beta_4 = \beta/4$ . This happens if, for a common channel length, the gate width if  $M_1$  is one-quarter of the other transistors, i.e.,  $2.5\mu$  in the present design.

The theoretical performance of the HCCM is not borne out in practice. The higher than expected  $V_0(min)$  can be attributed to the fact that the drain current of  $M_6$  exceeds  $I_R$ , because its drain voltage is greater than that of  $M_2$  by  $V_{on}$ , and thus the gate-source voltage of  $M_5$  exceeds the theoretical value ( $V_T + \sqrt{2I_R/\beta}$ ).

In the current saturation region, the design figure of unity for the DC current transfer ratio is closely met by the CCM and MWCM but not so well with HCCM. This is attributed to the unequal drain voltages of M<sub>2</sub> and M<sub>4</sub>.

Figure 3.12 DC output characteristics of the CCM

Figure 3.13 DC output characteristics of the MWCM

Figure 3.14 DC output characteristics of the HCCM

#### 3.2.2 Incremental performance

The incremental output resistances of the these circuits should all be similar and given by,

$$R_o \cong \mu(1+\chi)r_{ds} \tag{3.9}$$

Substituting simulated data, this gives  $R_o \approx 37.6 \mathrm{K}\Omega$  for the CCM compared with a value of  $38 \mathrm{K}\Omega$  (91.597dB with respect to a reference value of  $1\Omega$ ) in Fig.3.15(a) The values for the MWCM and HCCM are, respectively,  $35.76 \mathrm{K}\Omega$  and  $41.02 \mathrm{K}\Omega$ . In all of these circuits the input drive current was supplied by an ideal current source for test proposes. The use, in practice, of a non-ideal current source does not affect the output resistance of the CCM and HCCM but it does have a major effect on the MWCM because the drive current is in the feedback loop. Thus, suppose the resistance of the current drive circuit is  $r_{ds}$ , i.e., the same as the output resistance of a simple CM. Then the loop-gain magnitude, |LG|, in the MWCM is reduced by 50% and, with it, the output resistance because it is given by (Output resistance without feedback  $\times |LG|$ ). The drive current output resistance could be increased by making it that of a p-channel Wilson configuration but that is at the expense of greater circuit complexity.

The input impedances for the CCM, MWCM and HCCM shown for comparison, respectively, in Figs3.14, 3.15, 3.16 all display a fall-off in |Z<sub>o</sub>| of approximately 20dB/decade between 100MHz and 10GHz, indicating that, to a first approximation, they can be modelled by a resistance in parallel with a capacitance. However, because of the different values of |Z<sub>o</sub>| at low frequencies, they exhibit differing cut-off frequencies. The effective output capacitances calculated from them are 9.84fF, 10fF, 5.17fF for, respectively, the CCM, MWCM and HCCM. Those for the CCM and MWCM are comparable with a figure of 8.16fF obtained by substituting parameter data into the expression for output capacitance derived in Appendix3.1

Analysis and Design of High-Transconductance RF MOSFET Voltage-to-Current Converters

$$C_o \approx \frac{2C_{gs}}{(1+\mu)} + 2C_{gd} + C_{db}$$

(3.10)

The output capacitance for the HCCM is somewhat higher than the 4fF expected of a common-gate-output stage.

In this case the current in the  $C_{gs}$  of the output MOSFET is not magnified by current-mirror action as it is for the CCM and MWCM.

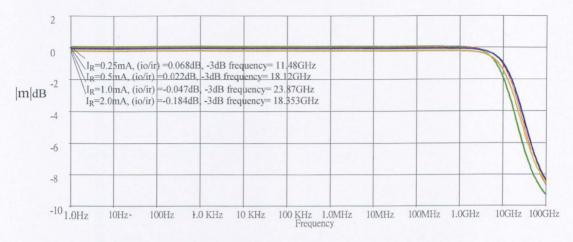

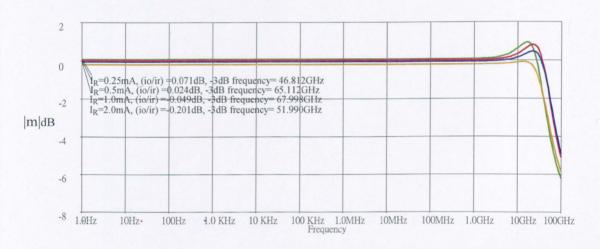

The frequency response of the small-signal current gain magnitude, |m|, is shown in Figs3.18, 3.19, 3.20 for the three types of CM under review.

A simplified equivalent circuit for the calculation the incremental short-circuit value of |m| for the CCM is shown in Fig.3.21

Figure 3.15 Zo in (a) dB and (b) phase of the CCM:  $V_0=1.5V$ ;  $I_R=1mA$

Figure 3.16 Zo in (a) dB and (b) phase of the MWCM:  $V_0=1.5V$ ;  $I_R=1mA$

Figure 3.17 Zo in (a) dB and (b) phase of the HCCM:  $V_0=1.5V$ ;  $I_R=1mA$

Figure 3.18 Current gain magnitude vs. frequency for the CCM

Figure 3.19 Current gain magnitude vs. frequency for the MWCM

Figure 3.20 Current gain magnitude vs. frequency for the HCC

Figure 3.21 Circuit for finding  $|\mathbf{m}| = i_0/i_i$  for the CCM

This resembles the circuit for the simple 1:1 CM but, in this case, the capacitance in parallel with  $2C_{gs}$ , in the input, is  $2C_{gd}$  instead of  $C_{gd}$  because of 'Miller magnification' of the  $C_{gd}$  of  $M_4$  in Fig.3.9

The -3dB cut-off frequency is given by,

$$f \cong \frac{(g_m + g_{ds})}{2\pi (2C_{gs} + 3C_{gd} + C_{db})}$$

(3.11)

Substituting measured capacitance values,  $(2C_{gs}+3C_{gd}+C_{db})$  =39fF and for operation at 1mA,  $1/(g_{ds}+g_m)$  = 157  $\Omega$ .

Hence,

$$f \approx 25.6 \text{GHz}$$

(3.12)

This value of f is in fair agreement with the observed value of 23.87GHz.

In the case of the HCCM the -3dB cut-off frequency is somewhat lower, at 22.4GHz, because the gate terminals of three MOSFETs are connected together rather than two. For the MWCM there is peaking in the frequency response of |m|, for some values of I<sub>D</sub>: this would be attributed to complex poles in the expression for loop-gain. This was not investigated further, for reasons given in the concluding section of this chapter.

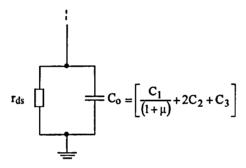

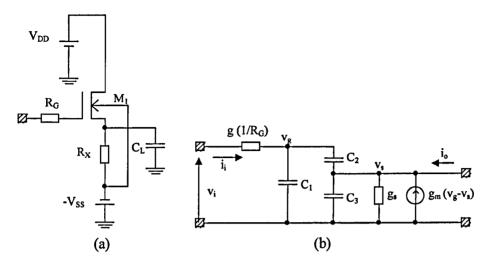

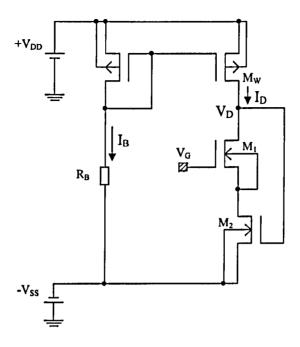

#### 3.3 Source-Follower

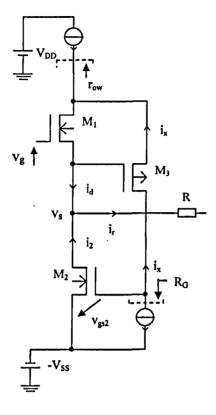

In this section the simulated performance of the source-follower under anticipated operating conditions is examined to see what simplifications, if any, can be made in modelling it for use in calculations for an initial paper design of V-I circuits incorporating it.

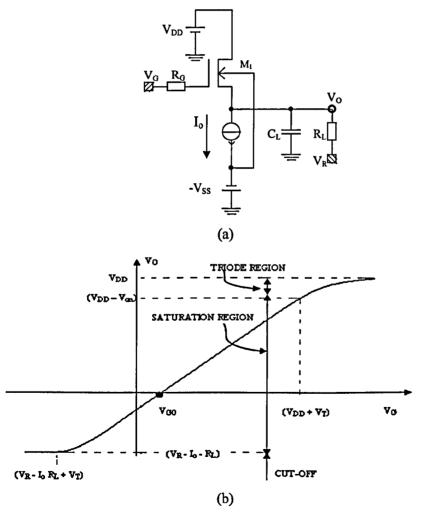

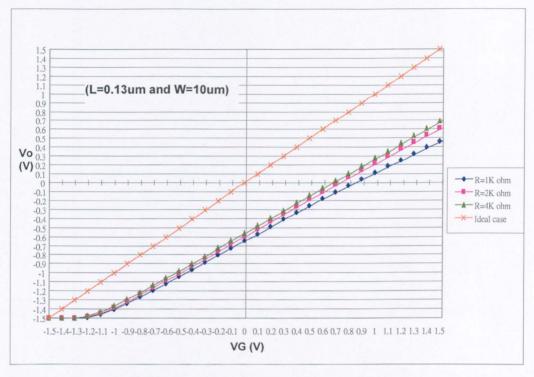

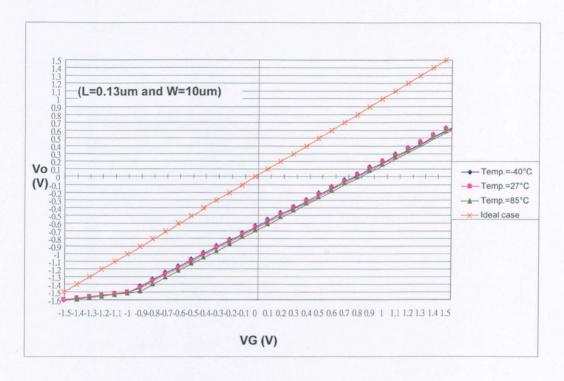

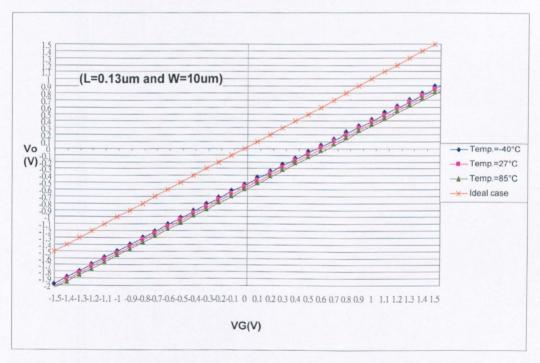

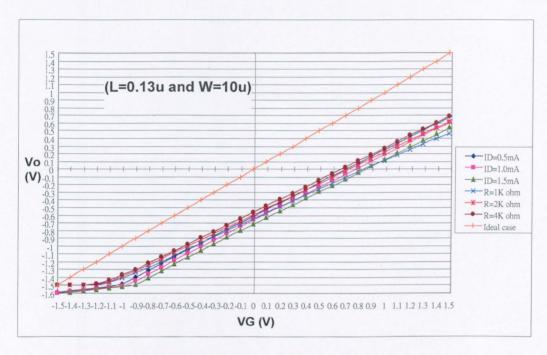

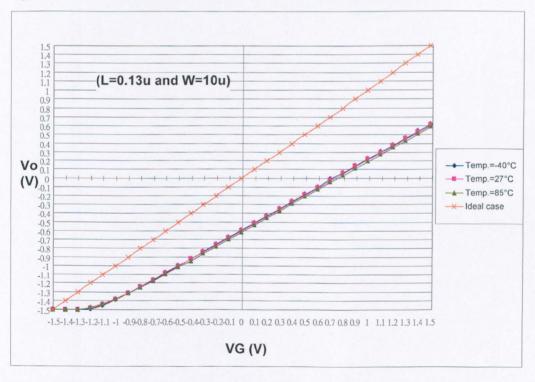

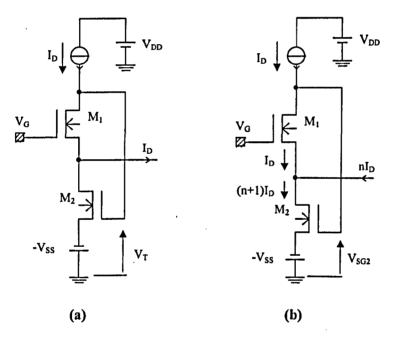

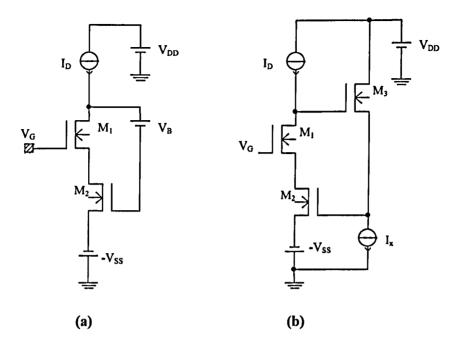

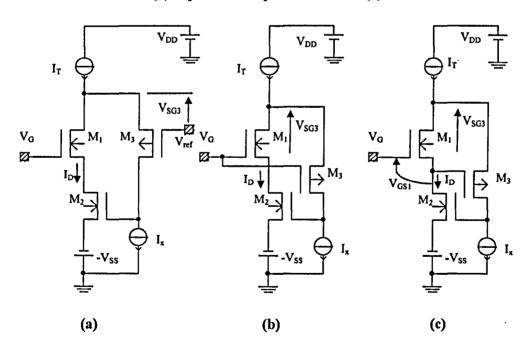

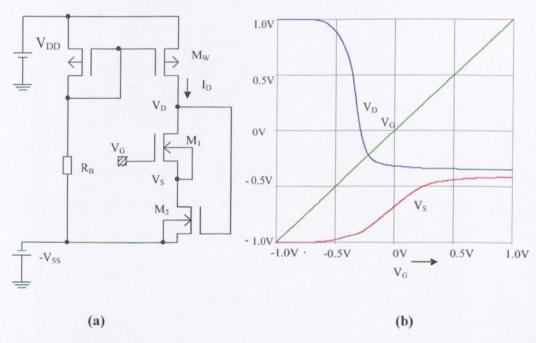

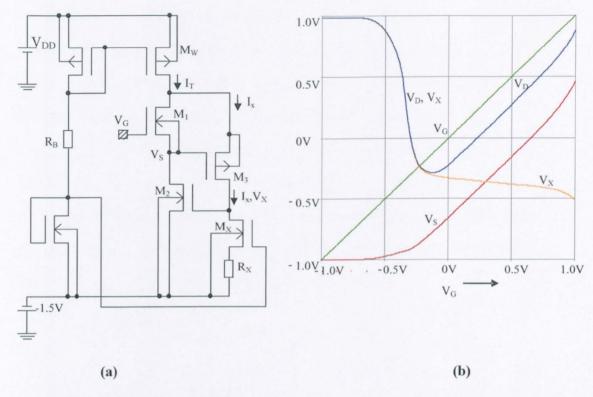

#### 3.3.1 DC characteristic

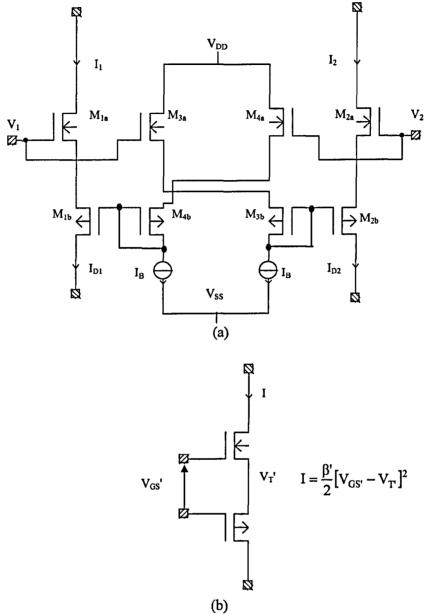

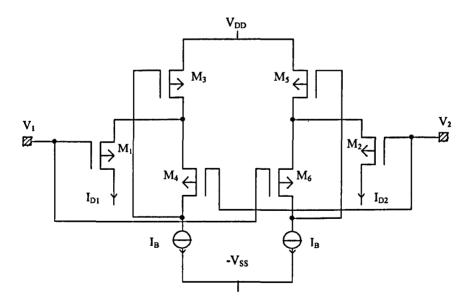

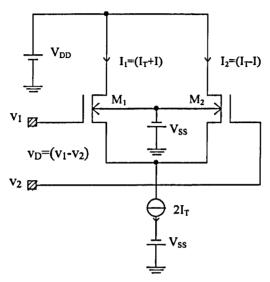

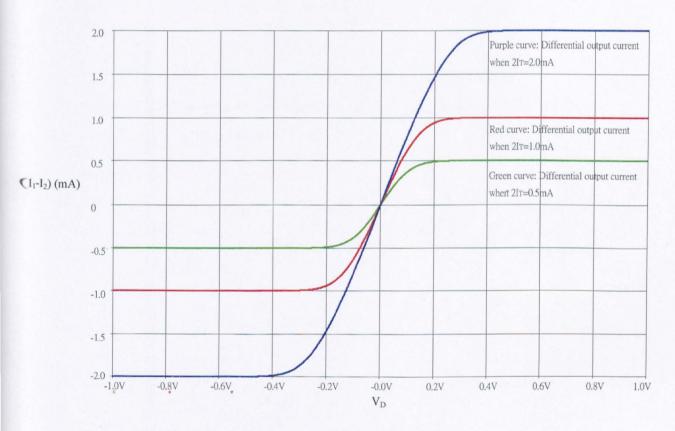

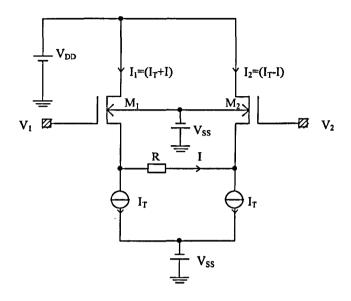

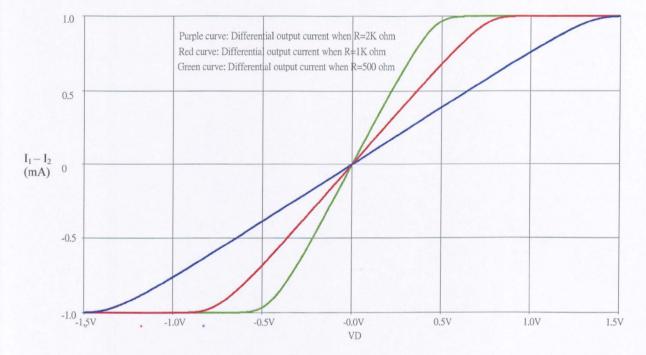

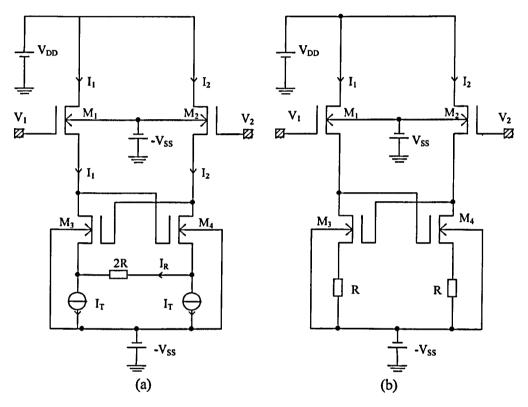

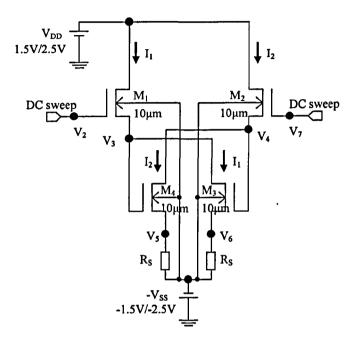

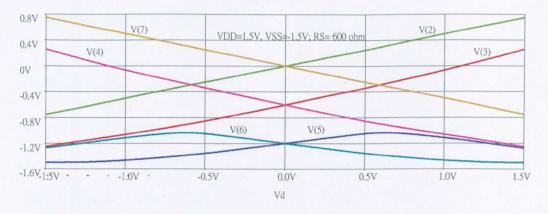

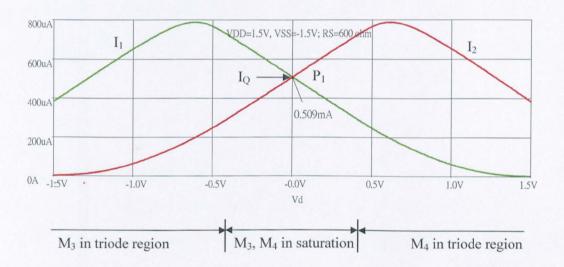

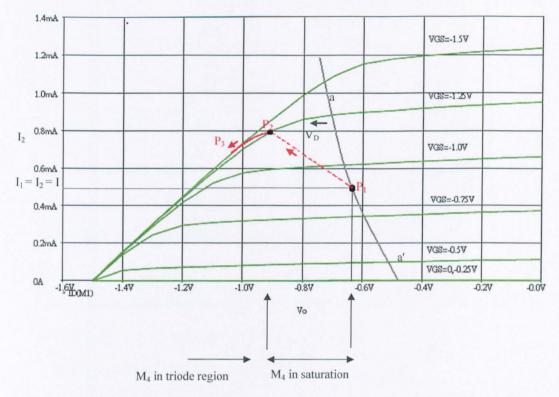

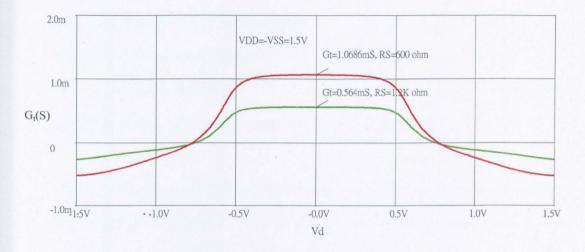

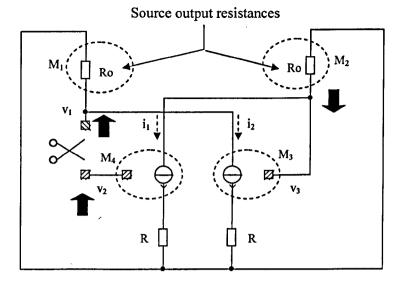

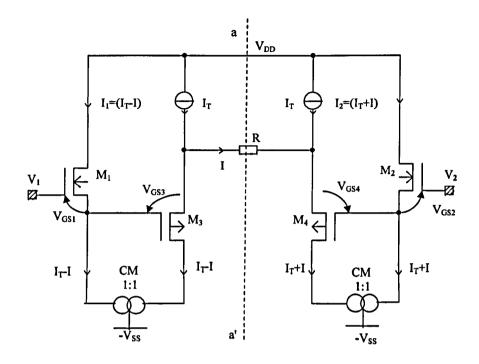

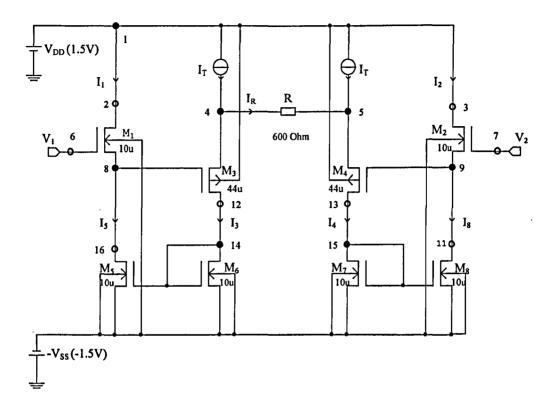

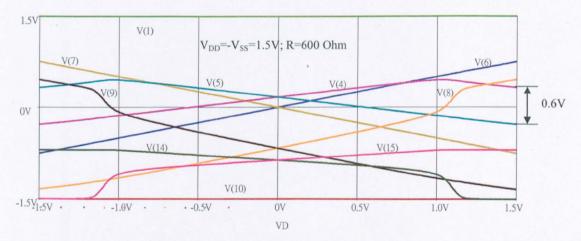

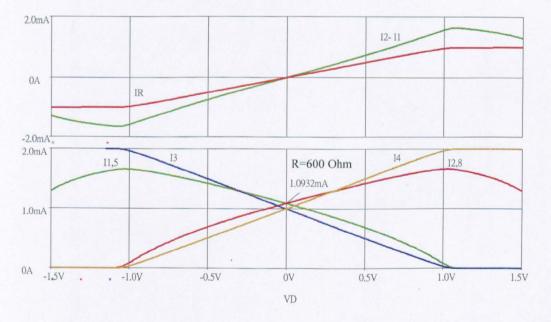

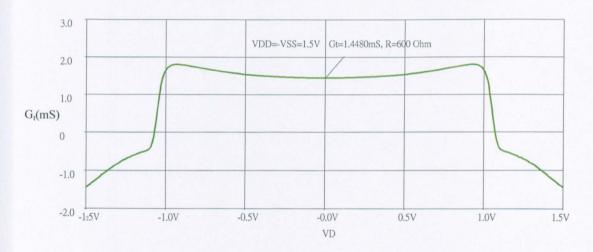

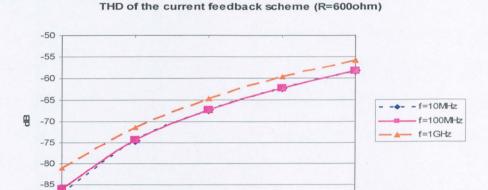

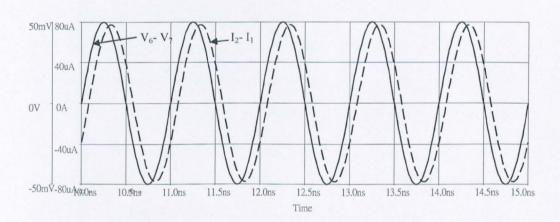

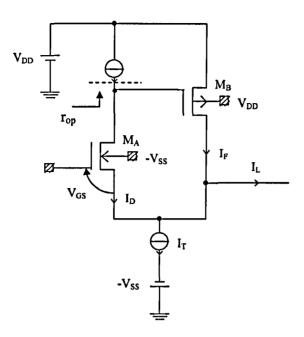

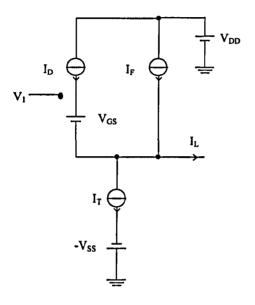

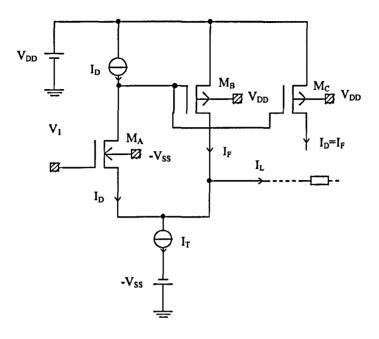

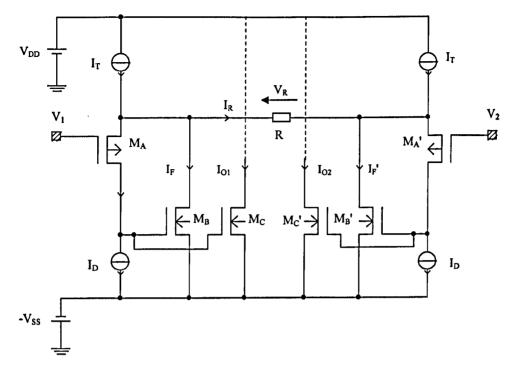

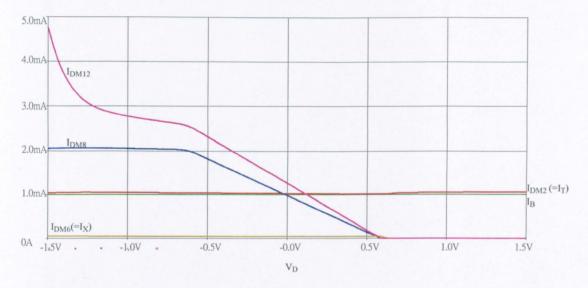

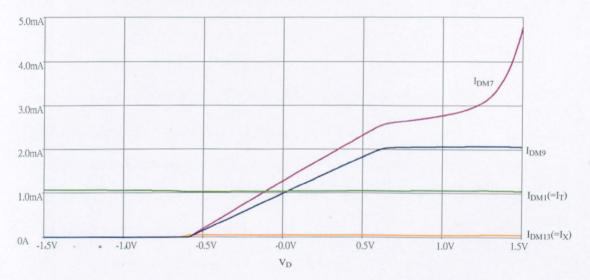

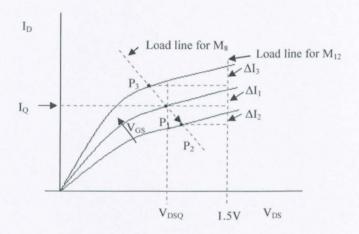

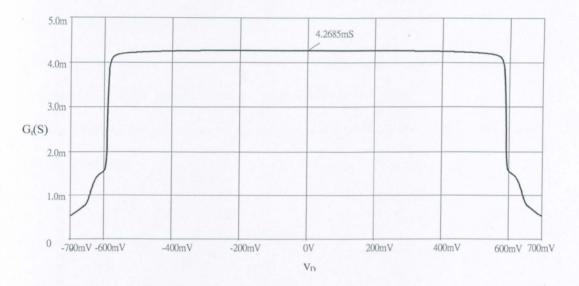

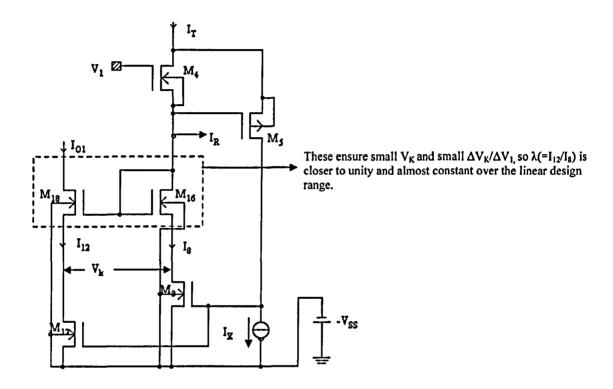

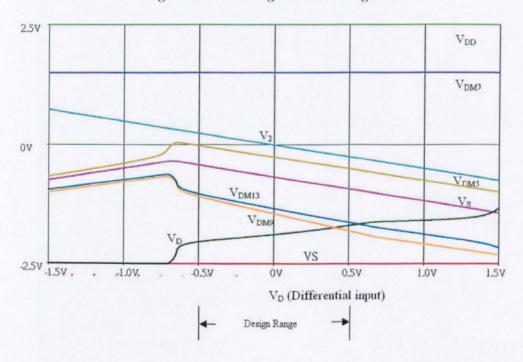

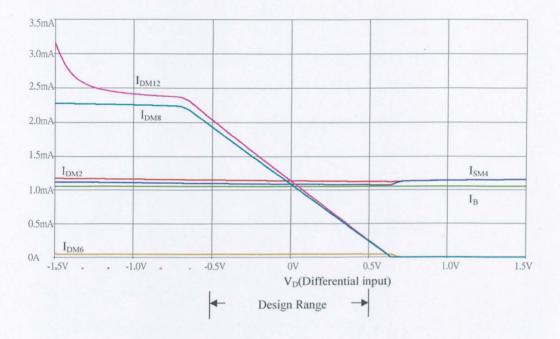

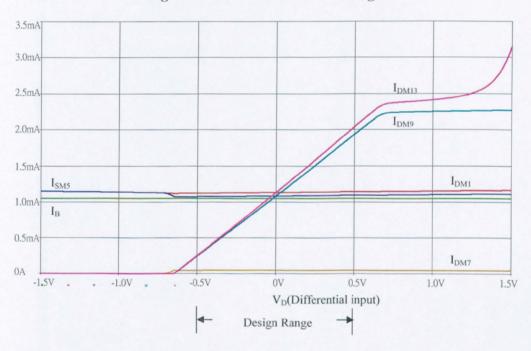

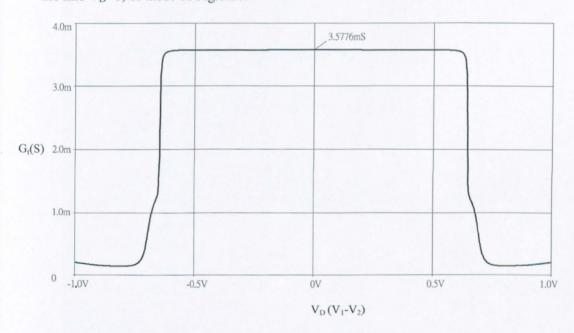

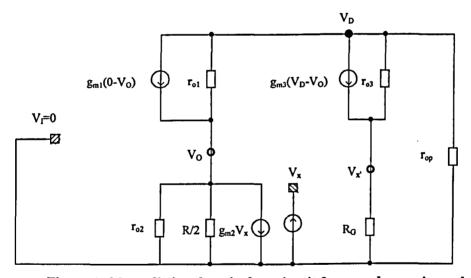

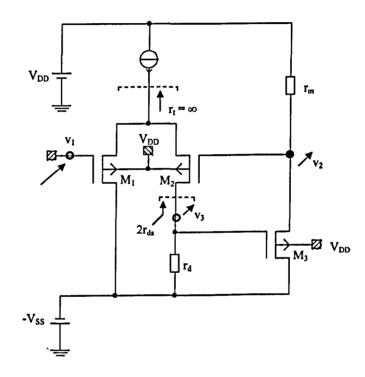

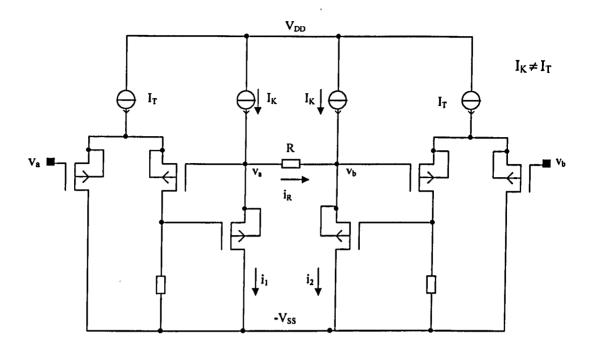

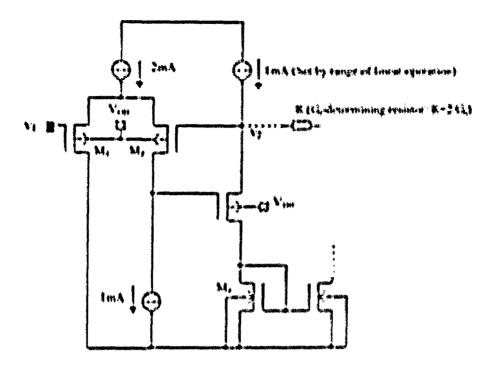

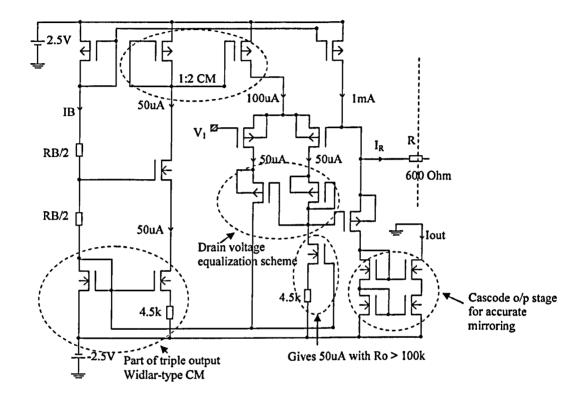

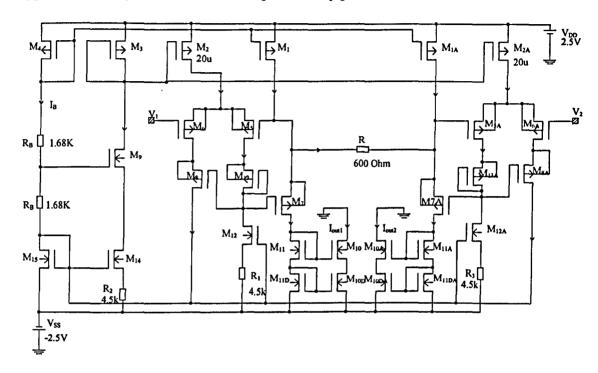

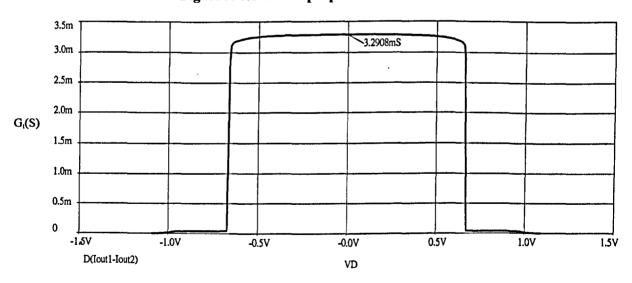

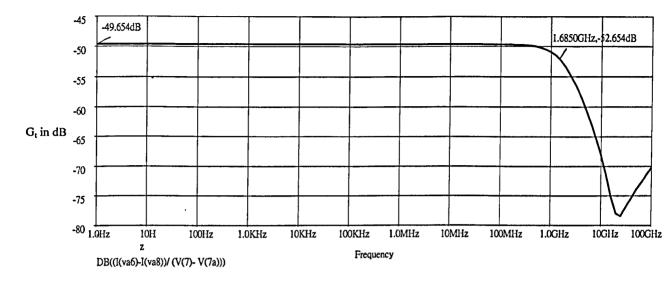

In the generalised N channel source-follower circuit of Fig.3.22(a), the load resistor  $R_L$  is connected to a chosen reference voltage,  $V_R$  (>- $V_{SS}$ )