1

# Zero-Maintenance of Electronic Systems: Perspectives, Challenges, and Opportunities

Richard McWilliam, Samir Khan, Michael Farnsworth, Colin Bell

Abstract—Self-engineering systems that are capable of repairing themselves in-situ without the need for human decision (or intervention) could be used to achieve zero-maintenance. This philosophy is synonymous to the way in which the human body heals and repairs itself up to a point. This article synthesises issues related to an emerging area of self-healing technologies that links software and hardware mitigations strategies. Efforts are concentrated on built-in detection, masking and active mitigation that comprises self-recovery or self-repair capability, and has a focus on system resilience and recovering from fault events. Design techniques are critically reviewed to clarify the role of fault coverage, resource allocation and fault awareness, set in the context of existing and emerging printable/nanoscale manufacturing processes. The analysis presents new opportunities to form a view on the research required for a successful integration of zero-maintenance. Finally, the potential cost benefits and future trends are enumerated.

Index Terms—Fault-tolerance, self-repair, zero-maintenance, built-in fault detection, self-healing systems

#### I. INTRODUCTION

The rising maintenance costs facing today's high value manufacturing industry is fuelling a new appetite for design strategies that reduce maintenance, repair and overhaul costs of complex high value systems [1]. The availability and dependability of electronic components and sub-components within complex, high-value systems is a critical driver for reducing the net cost per hour of operation. Fault events and associated system error states incur punitive costs due to; fault location and diagnosis; invasive inspection and test; provision for frequent maintenance intervals even if fault events have not occurred. Electronic systems and sub-systems have therefore become a pivotal element in fault-sensitive, service-driven sectors.

This article surveys several journal articles, conference papers, books and literature reviews on hardware approaches that are anticipated to pave the way towards zero-maintenance capabilities. Such capabilities are difficult (or evenimpossible) to implement exclusively within the software, mechanical or materials domains: instead the majority of strategies are partially (or fully) coupled with electronic systems and subsystems since this permits a wide range of fault mitigation

- R. McWilliam is with the Department of Mathematical Sciences, Durham University

- S. Khan is with the Department of Aeronautics and Astronautics, University of Tokyo. E-mail khan@ailab.t.u-tokyo.ac.jp

- M. Farnsworth is with the Department of Automatic Control and Systems Engineering, University of Sheffield, Sheffield, South Yorkshire. E-mail m.j.farnsworth@sheffield.ac.uk

- C. Bell is with the Department of Mechanical Engineering and Mathematical Sciences, Oxford Brookes University

Manuscript received xx xx, 20xx; revised August 26, 2017.

approaches. Hence cross-domain strategies feature heavily in the methods considered. The aim of this work is therefore to develop a core understanding of zero-maintenance within electronic systems and related design strategies for its implementation. This is achieved through a number of objectives outlined below:

- Analyse current trends in the evolution of self-recovery and self-repair towards achieving zero-maintenance;

- Present a quantitative (and where possible qualitative) comprehension of the design trade-off factors and metrics;

- Develop a cohesive understanding of zero-maintenance as a design approach and technology in its own right;

- Develop an appreciation of the core merits of zeromaintenance through a sector-wise view of the technology.

The title of this article has been chosen carefully, because the use of the word *perspectives* implies a personal analysis and presentation on behalf of the authors. The authors' expertise range in the areas of diagnostic design, signal processing, maintenance, self-healing and machine learning; with significant focus on practical implementation rather than theoretical. Nevertheless, the article's contents will be of general interest to electrical scientists and engineers, because some of the more practical issues of implementing self-recovery and selfrepair capabilities are often not appreciated, let alone the costs attached to them. The focus is therefore towards detailing the philosophy of having zero-maintenance. The principal concepts of self-detection, fault masking/mitigation behaviour monitoring are analysed and categorised according to their design level implementations. Self-recovery in the presence of faults is an important step towards realising complex systems capable of maintaining their designed for function throughout their intended life-cycle. The other characteristic is that their common design metrics must be analysed in terms of fault coverage, resource allocation/cost and fault awareness set in the context of existing and emerging electronic manufacturing processes. To the best of the authors' knowledge, this is the first study which provides a detailed account on zeromaintenance systems and related system approaches. These accounts have been broken down into research questions, that are suggested together with their motivations in Table I. The questions are aimed to make some semantic distinctions which are important towards application. These can be divided in terms of approach (active or passive), methodologies, techniques, applications, implementation requirements and capabilities, cost implications and their impact.

TABLE 1

RESEARCH QUESTIONS

| Research question                                                                                     | Table(s)    | Motivation                                                                       |

|-------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------|

| What are the technological requirements for zero-maintenance?                                         | VI, XI, XII | Identify the types of implementation tools that can be used to accomplish a task |

| What approaches can be considered to achieve these capabilities?                                      | XIV, XV     | Identify the types of active and passive approaches                              |

| What kind of design methodologies can be used for zero-maintenance?                                   | XIII, XVI   | Identify how to systematically solve the problem                                 |

| What techniques can be used to provide built-in fault detection?                                      | III         | Identify the type of techniques or tests that can be used                        |

| What metrics can be used to estimate the cost implications?                                           | VIII        | Identify the most important key performance metrics                              |

| What are the challenges for a zero-maintenance philosophy on mission-critical and resilience systems? | XVI         | Identify opportunities for self management systems                               |

| What kind of applications can benefit from its successful realisation?                                | XVII        | Categorise the applications where it can be used                                 |

#### A. Contributions

The article focuses on an emerging and important topic across many complex engineering industries. It provides a broad overview of self healing and self repair techniques, which span multiple application domains. For each technique, the authors provide its basic form and then consider how it can be useful to achieve zero-maintenance. Literature developments are discussed accordingly. This template provides an easier and succinct understanding of these techniques, taking note of their applicability and limitations. Whilst most of the work covered focuses on the electronics industry, there is an increase interest from electro-mechanical domain. The authors have noted that zero-maintenance systems need to attain the characteristics of self-diagnosis, self-repair and self-immobilisation to some degree, to prevent more serious damage and catastrophic breakdowns. As research within this area is of practical importance, some older references have been included, e.g., early discussions about online self-test and repair, which never really took hold after electronics became repairable during manufacture and relatively robust in-service. This is not necessarily true of emerging non-CMOS technologies and so the online repair theme is *popular* once more. To accomplish the study aims and objectives, this research undertook a filtering process where the key main themes and subtopics (formalisms, design and strategies for zero-maintenance of electronic systems) were decided upon, and selected journals and conferences formed the bulk of material for review and analysis. These range from electronics, maintenance and repair, manufacture and more, all of which are directly related to self-recovery, self-repair and its maintenance application. To summarise the key contributions at the outset, the article provides:

- An organised and critical view of current and emerging trends towards achieving zero-maintenance;

- A state-of-the-art on common design techniques in terms of fault coverage, resource allocation/cost and fault awareness set in the context of existing and emerging electronic manufacturing processes;

- A discussion of the key performance metrics and their relevance within different application domains. This includes past methods that have seen renewed interest such as fine-grained device/interconnect redundancy;

- An overview of the potential impact upon mission-

- critical, high resilience systems whose useful lifespan depends on efficient, self-management of spare resources. There seems to be an over-emphasis on being able to deploy high-level models rapidly, without the need of an underlying technical expertise about the processing framework:

- Consideration is given to the relative effort needed for the successful integration of a zero-maintenance philosophy weighed against cost factors.

Also, the authors have written this article in a way, that can allow readers with a non-electronic background to gain an understanding of the zero-maintenance philosophy. The article first follows the trends towards zero-maintenance and discusses the challenges for its successful realisation in Section II. In Section III, a brief perspective on the quantification of zeromaintenance parameters is formed. Expanding upon this we delve into more detail on how this approach can be introduced into electronic systems, providing state of the art examples in Section IV. It also outlines recent approaches for quantifying the success and trade offs of these techniques using current metrics. The discussion then switches to focus upon design with an overview of the main active and passive methods for mitigating faults in electronic systems in Section V, before a look at how a number of design strategies can be undertaken to incorporate these techniques across a number of applications in Sections VI. Finally the paper looks forward, drawing conclusions about this emerging field, with an outlook on the opportunities and challenges that await.

# II. TOWARDS ZERO-MAINTENANCE

Can a system's maintenance effort be reduced to zero? Perhaps a more realistic question is: can a system operate as originally intended, all the time?

If a system (or service or component) operates without failing, and delivers the exact business function without any manual intervention, then there is some semblance of moving towards zero-maintenance. Even though this may only be a theoretical possibility, it provides a perspective to explore questions for bridging a knowledge gap. An ideal self-engineering system should be capable of repairing itself in-situ without the need for human decision (or intervention). This will have a significant impact on reducing the overall cost of the maintenance process [2]. However, the application of this

philosophy within engineering is a challenge and the authors aim to draw attention to the need for maintenance systems to have self-diagnosis and self-repair capabilities, built-in logic for self-reconfiguration and a cost weighted solution.

The concept embodies the idea of enabling applications and systems to achieve and sustain near-zero spend, and transform the traditional maintenance practices from 'Fail-and-Fix' to 'Predict-and-Prevent' and ultimately to a 'Fail-Proof' state. A classification of literature is presented in Table II with a direct link between the topic of interest and the concepts discussed and analysed within. These articles highlight that concepts such as self-healing and self-repair are predominantly designed at the component and material science level. Within all these applications, there are generic concepts of zero-maintenance. However, for safety-critical applications, such as aerospace or nuclear that operate in inaccessible environments (e.g. space, offshore), there is a need to have a system level of self-diagnosis and self-repair, if not self-immobilisation, to prevent more serious damage and catastrophic breakdowns.

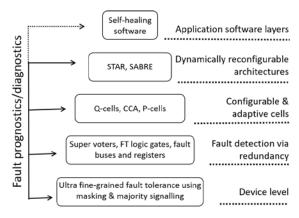

In the broadest sense, Reliability, Availability and Serviceability (RAS) performance metrics become highly dependent upon self-repair capability. Further downstream impact can be seen within integrated health monitoring, online self-test within which interrupt-free service is a critical profit margin driver [17], [18], [19]. As a result of this, growing interest has emerged for new design strategies with zero-maintenance properties. This article will focus on electronic components and sub-systems that are equipped with new fault detection and classification capabilities [20], [21]. Existing capabilities that can relate to these concepts are briefly introduced in Table III. Maintenance can be related to this emerging area of self-healing technologies as it links software and hardware mitigations strategies across multiple domains where many failure classes exist [22], [23]. Examples relating to electronic systems include mechatronics [24], control [25] and materials. In some cases an overlap exists between hardware and software domains occurs for example, in fault-tolerant GPU algorithms [26], VHDL methods for redundant layout in FPGAs [27] and FPGA bitstream manipulation [8] and therefore zero-maintenance is driven by a subset of failure classes. In addition to this, mitigation relies upon an awareness of the underlying hardware, especially multiple multiprocessor, custom configurable architectures and reliabilitydriven compilation [7]. This survey therefore focuses on key emerging trends for hardware-driven mitigation methods that relate to Table III.

# A. Technology platforms

The philosophy of zero-maintenance is relatable to several existing and emerging electronic technologies. State-of-theart hardware fault mitigation techniques handle permanent faults using active detect-respond mitigation, whilst sometimes operating along side passive masking. FPGAs are frequently used for studies in this area [6] where online reconfiguration remains a highly challenging task [12], [28], [29]. More sophisticated reconfigurable platforms are emerging that support development of dynamic self-test and repair (STAR). Manufacturing yield enhancement has been a strong driver for significant investment for silicon electronics and the resulting yield-driven strategies continue to extract fully functional operation out of essentially error-prone fabrication processes [30]. These strategies are undergoing a transformation to include built in repair mechanisms that operate beyond the point of manufacture. Emerging non-silicone technologies of relevance to zero-maintenance are printable large area and nanoscale electronics that bring new challenges and opportunities for fault mitigation due to their differing fabrication processes and technology scaling.

In respect to hardware development platforms, a key goal of future zero-maintenance strategies is to proliferate fault detection and discrimination towards the lower design levels in order that detection occurs closer to the actual fault locale. This aspect is explored further in Section IV-A. It is further expected that fault mitigation operates most effectively when concentrated as far as possible to the same locale. To support development of such fine-grained fault mitigation, hardware in loop monitoring has advanced significantly in recent years to support industrial control and monitoring platforms for highvalue sectors such as aerospace, mining, consumer transportation and exploration where even small down-time events incur considerable financial cost. In such cases the incorporation of built-in actions that inhibit further fault events become extremely valuable as does the ability to record the frequency and nature of abnormal events.

#### B. Implementation challenges

A precursor to eliminating effort required to maintain any function, is to monitor it. Under nominal operational conditions, dependability in electronic systems is secured when errors arising from faults can be diagnosed. Therefore fault detection and mitigation during normal operation becomes paramount. Faults stem from a number of sources, including production defects (infant mortality), ground level radiation effects, yield challenges for next generation fabrication processes, greatly increasing complexity of mission and safety critical electronic systems, testability of complex systems, highly integrated System in Package (SiP) ageing factors especially for high power devices and ultra low voltage ASICs. Within this survey, it is therefore assumed that the primary faults under consideration relate to transient upsets or permanent faults in each of these cases<sup>1</sup>. Therefore, several factors make achieving zero-maintenance a challenging endeavor:

1) Provisioning for various fault types: Commonly encountered faults and errors (potentially) arising within electronics are considered in Table IV. Such events may occur on a time-limited basis and maybe short-lived, repetitive (persistent) or periodic in nature. Upsets can cause temporary or permanent fault conditions, but errors do not necessarily result. Faults that do not cause immediate errors are termed sub-critical and may lie dormant between power cycles or remain indefinitely. Their influence upon error state is dependent upon the system state, and therefore sub-critical faults are

<sup>&</sup>lt;sup>1</sup>A broad discussion of such matters is found in [31], in which various examples of fault and error manifestation are discussed.

TABLE 2

CATEGORISATION OF REVIEW LITERATURE RELATING TO ZERO-MAINTENANCE PHILOSOPHY

| Торіс        | Article                          | Offlipe | online           | Chip             | Packas | Yield St. | Fault of | Fault       | Modrif      | Cellius redundanció | Recons      | EDC "Inguration | Fine-grains |

|--------------|----------------------------------|---------|------------------|------------------|--------|-----------|----------|-------------|-------------|---------------------|-------------|-----------------|-------------|

| Microsystems | [3]                              |         | X<br>X           | X<br>X           | х      |           |          | X           | X           |                     |             | х               | X           |

| wherosystems | [5]                              |         | X                | X                | А      | x         |          | x           | x           |                     |             | Λ               | x           |

| FPGA-based   | [6]<br>[7]<br>[8]<br>[9]<br>[10] | x<br>x  | X<br>X<br>X<br>X | X<br>X<br>X<br>X |        | х         | x<br>x   | X<br>X<br>X | X<br>X<br>X | X<br>X<br>X         | X<br>X<br>X | X               |             |

| Computer     | [11]                             |         | X<br>X           | x                | x      |           | X        | X           | X           |                     | X           | X               | x           |

| architecture | [13]<br>[14]                     |         | X<br>X           |                  | x<br>x |           | x        | x<br>x      | X<br>X      |                     | x<br>x      |                 |             |

| DRAM         | [15]                             | х       |                  |                  |        | х         |          | X           |             | X                   | X           |                 |             |

| Evolutionary | [16]                             | х       | X                | х                |        |           | х        | X           |             | X                   | X           |                 | X           |

TABLE 3

CURRENT METHODS FOR RESILIENT OPERATION

| Technique               | Context                                                              | Example of state-of-the-art                                                     |

|-------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Built-in self-test      | Perform off line integrity checks before commencing normal operation | Power-On Self Test (POST) within computer BIOS                                  |

| Online status reporting | Real-time fault checking                                             | General dashboard warning light                                                 |

| Fault discrimination    | System-level diagnosis via sub-module level BIT                      | Specific dashboard warning light                                                |

| Fault monitoring        | Detect and log fault occurrences                                     | SMART hard disk monitoring                                                      |

| Fault masking           | Typically majority voting within modular sub-system                  | TMR controller for safety critical plant systems                                |

| Active fault mitigation | Active response to eliminate faults within logic                     | Data scrubbing                                                                  |

| Self-preservation       | Prediction and mitigation against faults                             | Mostly found in electromechanical systems e.g., hard drive free-fall protection |

| Error mitigation        | Correct errors that cannot be eliminated by fault mitigation         | EDC for memory modules                                                          |

assumed to compromise system dependability. Critical faults cause immediate, persistent and potentially cumulative errors. Even so, there is no guarantee that errors will be immediately observable. The susceptibility to fault-induced upsets increases with various factors, such as increasing die area, shrinking transistor gate dimension and reduced switching voltage. These are all common drivers in microelectronics and future nanoscale and printable electronics hence significant research effort has been directed towards faults occurring within future ASICs, interconnects and memory devices, especially those faults induced by radiation particle strikes [32]. In many cases physics of failure (PoF) models are used to help predict the likely system response. This evidence is then used to build a case for provision of redundant resources to be allocated at design-time and weighing up additional cost.

2) Detecting faults: Considering board and sub-system levels, physical breakdown of printed circuit boards (PCB) is a major concern in high performance systems, especially for high-voltage applications. An example of a simple fault analysis of PCBs is summarised in Table V, where various symptoms and related processes of elimination that involve costly and time consuming design steps are characterised (see

also [33]). This classification exemplifies the complexity and effort associated with maintenance where, at the sub-system level, procedures for monitoring and assessing potential failures and mitigation strategies become increasingly complex. In critical applications, failure modes and effects analysis (FMEA) procedures may be employed at the system level to form predictive models for maintenance planning. This includes potential disruption caused by 'No Fault Found (NFF) scenarios and strategic provision of built-in test (BIT) logic [34]. Indeed, BIT logic is viewed as beneficial at board and system levels provided the additional complexity is feasible. An example of this is shown in Table VII, where the relative cost/benefit of BIT is estimated [35]. These factors contribute to the overall maintainability and availability of the system [36]. Potential causes of failures are typically assessed by system experts and preventative or corrective courses of action are determined. FMEA is less commonly applied to lowlevel design due to the complexity of analysing all subparts and hence is mostly confined to high-level integrity analysis. Degradation is also to be considered when designing zero-maintenance strategies; the onset of ageing may become accelerated in the presence of persistent faults hence mitigation

strategies offer the potential to slow this process by repair. Detection and monitoring is also extremely useful in demand-driven maintenance during the onset of ageing.

3) Responding according to fault severity: Systemic and device-level faults give rise to critical errors [37], while soft errors arise from a number of different fault conditions [38]. In particular, dormant fault and sub-critical faults can remain unnoticed for some time before causing errors. Further upset mechanisms include electromagnetic interference (EMI), thermal cycling and mechanical degradation of packaging. Faults may also manifest as incorrect logic levels appearing at gate inputs/outputs or else bit upsets within memory contents (or indeed the manifestation of incorrect voltages/current components within analogue circuitry). Different error behaviours are possible depending upon their location and duration [39]. Examples include: errors that are overwritten and do not cause failures; latent errors that persist but which do not cause output failure (but may affect internal states); and errors that are detected and corrected. A more complete model for the relationship between faults, errors and failures has been proposed in [31].

4) Integrated self-maintenance: Many faults manifest as flaws during manufacture and, while these must be removed during test and repair before the product is worthy of selling, there is potential to continue the process of detection and repair into the useful lifetime via runtime and POST maintenance. As a result of yield issues, many high-density ICs contain large pools of redundant elements that are partly consumed during production BIST, but the remaining redundant elements and associated BIT logic remain inactive thereafter [40]. Even after built-in test and repair (BISTAR), it is conceivable that noncritical faults may have been inadvertently triggered during resource reallocation and may compromise normal operation. BISTAR will continue to feature in future FPGAs [41], configurable ASICs [42] and nanoscale electronics [43] and it has been suggested that BISTAR logic could be made available for runtime test or repair of logic [44] and interconnects [45].

Due to the above challenges, achieving zero-maintenance, in its most generic form, is not an easy problem to solve. In fact, most current maintenance design techniques solve only specific formulations of the problem. These efforts are further influenced by rapidly changing technology requirements and availability as well as investment costs for development and test, factors that are often determined by the industry domain in which maintenance is required.

# C. Formalisms of zero-maintenance

In the context of this paper, zero-maintenance can perhaps be best viewed as a collection of capabilities that ensure error-free operation in the presence of faults occurring within an integrated sub-system or component, with minimal external intervention. This is also related to the area of autonomous maintenance wherein autonomous systems take on similar capabilities, for example the use of external robotic systems to perform specific maintenance tasks [46]. A number of related maintenance requirements can be identified within the literature, though most come from related areas. A synopsis

is given in Table VI including an indication of state of the art. At their most basic level, faults (and errors potentially arising as a result) are masked and/or removed such that their influence is no longer critical to error-free operation. Thus a minimum condition of zero-maintenance is that all faults are made sub-critical. By the same measure, it is also desirable to address sub-critical faults by masking strategies. Design for zero-maintenance therefore comprises fault-tolerant design augmented by active detect and response capabilities such that operational life is extended. Ideally fault-free operation is secured.

#### III. QUANTIFYING ZERO-MAINTENANCE

Several metrics have been considered for quantifying the performance of self-maintenance strategies. Their design-time prioritisation is application-dependent and each must be evaluated in terms of their reliance upon redundant and coordination resources. Moreover, such resources must be allocated at design-time. Existing metrics are summarised in Table VIII, including fault capacity and performance impact. There are few real-world examples where evaluation of these parameters has been reported in the open literature although some detailed FPGA studies have been summarised in [8].

An important step in the design process is test and evaluation of the detection and mitigation strategy. Ideally this would be done within the actual hardware under test where emerging fault detection and mitigation strategies will aid with the test and verification of complex electronic systems. An example of this is the Slackprobe design for ARM processors that places embedded logic deep within strategic locations of the chip for critical timing monitoring. This logic is included within synthesis/layout steps and provides new insights into ageing effects as the timing becomes degraded. In may cases however the overhead associated with the test logic is high and data collected is not directly related to fault events. Besides embedded hardware monitoring, an alternative approach is to implement fault injection engine during the design evaluation phase. Fault injection is a more aggressive approach that emulates direct fault conditions at the hardware level under the control of a fault injection engine [52]. For low pin count ICs, hardware electronic faults may be injected directly. Highdensity devices such as ASICs and FPGAs require dedicated internal logic [53], [54]. A comprehensive description of fault injection techniques can be found in [55]. Fault injection has also been discussed at the transistor, gate, device and system level with in ASICs [56] but interconnect-related faults are not as well understood and further work is needed especially for self-repairing strategies [8].

Despite benefiting from mature software tools FPGAs are not optimised for on line reconfiguration. Fine-grained Triple Modular Redundancy (TMR) requires special considerations as discussed in [27]. Off-the-shelf solutions do exist that exploit either partial-reconfiguration facilities or else direct manipulation of the configuration bitstream. Several methods also exist for testing the resilience of FPGA strategies including stuck-at-faults, bitstream analysis, radiation testing and fault injection characterisation [10].

TABLE 4

FAULTS OCCURRING WITHIN INTEGRATED CIRCUITS

|           | Abbr.                                   | Definition                                                                                                                          | Description                                                                                                                                                                                                                                                |

|-----------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transient | SEU<br>SET<br>SBU<br>MBU<br>MCU<br>SEFI | Single event upset Single event transient Single bit upset Multiple bit upset Multiple cell upset Single event functional interrupt | Single transient fault event Transient pulse affecting gates and latches Logical bit inversion within register/memory Multiple register bits inversions Faults manifesting/propagating within logic cells Produces observable failure at cell/block output |

| Permanent | SHE<br>SEL<br>SESB<br>SEB<br>SEGR       | Single hard error Single event latch-up Single event induced snap-back Single event burnout Single event gate rupture               | Caused by single fault, commonly stuck-at Rail to rail short circuit in pnpn circuits Rail to rail short circuit in nMOS circuit Thermal runaway in power transistors Breakdown of gate dielectric                                                         |

TABLE 5

ESTABLISHED METHODS FOR PCB LEVEL TESTING AND REPAIR WITHOUT SELF-REPAIR STRATEGIES (ADAPTED FROM [33]).

| Fault type                   | Cause of failure                                                                            | Eliminated by                                            | Failure model                |

|------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------|

| Layout                       | Crosstalk, grounding, power rail noise, fan-in or fan-out violations                        | Correct application of layout rules                      | Stuck-at, intermittent       |

| Construction                 | Inappropriate interconnect design<br>or packaging, solder splash, bridg-<br>ing, dry joints | Careful construction and inspection                      | Stuck-at, bridging           |

| IC internal failures         | Fabrication defect, yield issue, packaging defect                                           | Careful construction, screening                          | Stuck-at, metal-metal shorts |

| Environment                  | Accelerated component degradation                                                           | Use components qualified for envi-<br>ronment conditions | Stuck-at, intermittent       |

| Degradation (time-dependent) | Component ageing, modifications                                                             | Preventative maintenance                                 | Stuck-at                     |

| Design and implementation    | Critical races, static/dynamic errors, hazards                                              | Correct design and validation                            | Stuck-at, intermittent       |

$\label{table 6} TABLE~6$  Related maintenance requirements reported in the electronic domain

| Method                        | Aim of strategy                                                                                                                 | State of the art                                                            |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Built-in self-test            | Detection of fault caused by upset at power-on and/or run-time                                                                  | Automated SMART disk reporting [47]                                         |

| Fine-grained fault masking    | Fault masking at device level, possibly including fault identification                                                          | PaNDA chip [42]; interleaved logic; Gaisler Processors [48]                 |

| Built-in self-reconfiguration | Capability for online or offline design reconfigura-<br>tion                                                                    | Many lab demonstrations, but unclear whether used commercially              |

| Built-in self-reallocation    | Self-initiated reorganisation of logic fabric                                                                                   | Fundamental research                                                        |

| Robust state machines         | State machine encoding for fault resilience                                                                                     | Adopted in commercial designs                                               |

| Self-maintenance              | Correction of faults in-service (active operation or in standby). May initiate partial repair until next scheduled maintenance. | Some commercial examples but mostly fundamental research                    |

| Survivability                 | Continuously recover from faults, consuming resources as necessary (possible at expense of performance)                         | Systems for long-term space exploration                                     |

| Self-diagnosis                | Ability to determine most effective course of action; reporting of remaining repair capacity.                                   | Some software-based techniques [49]; MEMS integrity test [50]               |

| Self-preservation             | Able to reduce the impact of fault condition before major action is required                                                    | Primarily electromechanical systems e.g., disk drive shock protection [51]. |

TABLE 7

COST/BENEFIT FOR BIT, VIEWED FROM VLSI PERSPECTIVE ADAPTED FROM [35]. + COST INCREASE, - COST REDUCTION, +/- COST INCREASE LEADING TO SAVING.

|         | Redign, test | Fabrication | Production testing | Mainte-<br>nesting | Dipgnosis, | Seviception |

|---------|--------------|-------------|--------------------|--------------------|------------|-------------|

| Chips   | +/-          | +           | -                  |                    |            |             |

| Boards  | +/-          | +           | -                  |                    | -          |             |

| Systems | +/-          | +           | -                  | -                  | -          | -           |

TABLE 8

Key performance metrics for assessing zero-maintenance strategies

|            | Metric                       | Description                                                                                                                            |

|------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|            | Fault coverage               | Refers to fractional area of overall circuit that protected and diversity of faults that can be handled                                |

| se         | Fault granularity            | Minimum design layer at which faults can be detected/addressed                                                                         |

| Response   | Fault capacity               | Number of remaining faults that can be sustained by mitigation strategy                                                                |

| Re         | Performance reduction        | Loss of application performance due to zero-maintenance opera-<br>tions                                                                |

|            | Latency                      | Time required for recovery                                                                                                             |

| es         | Resource overhead            | Number of additional components needed over and above basic design                                                                     |

| Resources  | Resource re-use              | Achieving efficient consumption of redundant resources (active methods)                                                                |

| Res        | Energy usage                 | Energy consumed during recovery and consumed by additional resources overall                                                           |

| stic       | Reporting Remaining lifetime | Discrimination & reporting of fault events at multiple system levels Indication of remaining operational hours after which faults will |

| Diagnostic | Kemaning metine              | no longer be handled                                                                                                                   |

| Dis        | Logging                      | Capacity to store a log of fault history and classification                                                                            |

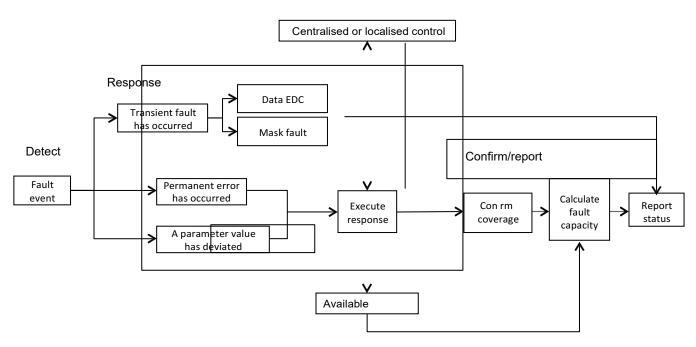

# IV. DESIGN MODELS FOR MITIGATION

Mitigation strategies take the form of either distributed passive masking or active detect and respond. As noted earlier, some are already utilised in manufacturing test and repair and, to a lesser extent, degradation management. In the former case detection followed by repair is sometimes referred to as built-in test and repair (BISTAR). There is a large class of platforms based on reconfigurable FPGAs and PLDs that are explored later in this section. An important question is how can the mitigation strategy determine the most appropriate level of response? A sub-component that is affected by transient upset will not benefit from active response capability since unless permanent effects result; repairing temporary faults by reallocating valuable redundant resources is extremely inefficient and would not address further occurrences of transient upset. Fault masking would be the primary design strategy in this case. In other cases however, the decision is less straightforward because both transient and permanent fault handling may be expected to occur and hence resources must be traded against design overall cost/benefit factors. In [57] general considerations of early fault-tolerant computers were explored and a number of questions raised: when should fault tolerance be considered? How do errors manifest, human error, software fault or hardware fault? How is the benefit quantified? As stated earlier, the motivation for fault-tolerance has shifted from manufacturing consistency toward random and cumulative faults caused by environmental and ageing factors.

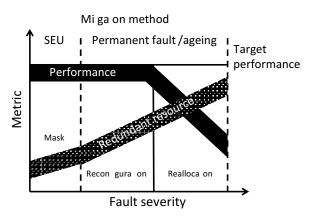

To help set the context for design for zero-maintenance a suggested relationship between fault severity and design mitigation as given in Fig. 1 for a non-specific sub-component. A similar view was suggested by Noura et al in the context of resilient control systems [25]. The view presents several typical design considerations: the absolute of limit of fault tolerance, the regions of applicability for each class of fault handling and the performance degradation for more sophisticated

Fig. 1. Progressive strategy for fault-tolerant mitigation with performance impact (adapted from [25]).

fault handling procedures. The anticipated impact on sub-component performance somewhat qualitative, but is indicative of the benefits of employing more complex maintenance strategies. Resource restructuring is a simple concept, but in practice involves a complex hardware reorganisation process that requires coordination and accurate fault diagnostics. This tends to become especially complex for current reconfigurable FPGA designs such as STAR (self-test and repair) [58] that is capable of detecting and isolating faulty logic by activating spare logic, but which requires significant external processing resources.

# A. Passive methods

Significant advances in electronics fabrication and packaging methods have taken place over the past decades and the perceived reliability and dependability of resulting ASICs is high. In recent years a re-emergence of passive mitigation has occurred in part to a response to new nanoscale electronics but also the onset of SEUs within current-generation ASICs. The most prevalent passive fault-tolerant strategy is n-modular

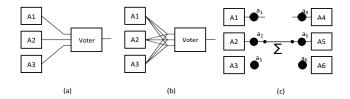

Fig. 2. Majority strategies for fine-grained redundancy. (a) basic majority using logical voter (b) full majority logical voter (c) weighted analogue majority signal formed by summation of weighted contributions. In this example output of each module  $A_1$ ,  $A_2$ , ...,  $A_6$  is weighted according to  $a_1$ ,  $a_2$ , ... $a_6$ .

redundancy (nMR) involving majority signalling. An early review of nMR design considerations for computer hardware is provided by Carter [13] while fundamental nMR concepts may be traced back to the much-cited work of Von Neumann [59] that was inspired by solutions observed in biological systems that construct resilient systems out of many spare components. Each component is assumed prone to failure and hence error-free operation is secured in the presence of faults through massively redundant node, interconnections and majority signal blocks. Various majority signalling methods have been proposed including partial and full majority (Fig. 2a-b) and summing (Fig. 2c). More recently, fault masking has again arisen as a key approach in nanoscale design but for now utilising small n [60]. Numerous variations on this theme exist, each bringing their own performance / resource trade-off at the fine-grained transistor or logic gate levels.

The potential impact on availability and cost of ownership brought about by fault masking is considered further by Maxion [14]. Proven fault handling measures include selfpurging [61], where the classical nMR with voter structure is modified to provide explicit fault detection and isolation of each module. The required switching mechanism constitutes a departure from purely fault masking to detect-isolate actions. In this case the overall reliability is highly dependent upon the individual switching reliability. Further augmentations to the TMR approach were suggested in [39] to include explicit detection and handling of transient and permanent errors. In this scheme, fault detection and self-reassertion of the correct logic state is possible within individual modules. In addition detect-isolate is performed when a permanent fault occurs in a single module, in which case the design reverts to a master/checker scheme. Although this implementation does not include a full self-reconfiguration implementation, it is attractive because there is minimal logic overhead in comparison to the conventional TMR implementation. Of course, the high resource overhead of the TMR scheme itself is still present.

Graceful degradation is difficult to achieve by passive methods due to the inherently limited fault capacity. Although detection is not directly involved, it is possible to extract and utilise majority signals for basic diagnostics. This is done at the modular level to generate enumerated states such as 'ok', 'fault has occurred but still ok', 'cannot tolerate further faults' (critical condition) and 'unavailable'. Although feasible at the modular sub-system levels, their implementation requires considerable design effort at lower levels (i.e. closer

to the origin of fault) and hence new architectures are needed to support this level of granularity. The benefits are clearly significant for integrity monitoring in the presence of transient upsets.

1) Bottom-up design methods: Fine-grained strategies have seen specific interest recently owing to concerns over the vulnerabilities of emerging nanoscale and to some extent state-of-the-art printable electronics. At the lowest design levels, provisioning of redundant transistors has been discussed for compensating yield tolerance occurring during manufacture [62]. Such strategies inevitably involve compromises, namely redundancy overhead, complexity of fault detection and degradation of performance through the use of nonoptimal transistors. However, within the zero-maintenance paradigm the benefits of graceful and predictable degradation and self management of faults are extremely attractive. At the sub-system level, online fault discrimination and monitoring operates at the modular level and within maintenance-heavy products, such as land, air and space vehicles, it becomes possible to monitor component aging via key response factors that that are expected to degrade more progressively over time [2]. These methods focus on self-correction of stuckat faults within nanoscale logic units, for which there are two reasons to consider fine-grained redundancy: firstly, fabrication processes are more prone to defect and variability [63] and the high density of nanoscale manufacturing exacerbates the challenge of high volume production. Secondly, the reduced device dimensions will result in increased susceptibility to inservice faults. With the advent of Large Scale Integrated (LSI) ICs, fine-grained redundancy was employed in mission critical electronic systems such the flight computer of the Apollolunar mission. Its use was ultimately restricted due to improvements in manufacturing tolerances and the unfavourable view of maintenance at the time [64]. Increasing component density brings a number of issues relating to upset vulnerability and manufacturing defect that must be reduced so that these technologies are able to complete with current silicon technologies. Further considerations include reduced operating andthreshold voltage that, together with higher feature density, will lead to lower SEU immunity. Defect mitigation commands the highest effort in the first instance [31] but a number of approaches nonetheless been reported in recent years as summarised in Table IX.

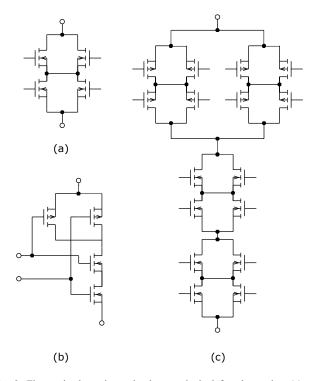

nMR has also been incorporated within FPGA configurations at the block level [65], extended to fine-grained gate redundancy by a method closely related to quadded logic[60] and ultimately appearing at the transistor level via N-modulo redundancy (nMR) [66] and most commonly TMR implementations [67]. A further variation involves *scrubbing* in which the configuration is periodically refreshed from a golden bitstream [68]. This method is very popular due to its simplicity although service interruption does occur. In [43], multiplexed redundancy was considered at the lowest design levels to improve the reliability of logic gates. Future space exploration will further leverage fine-grained strategies wherever possible, principally because of the additional complexity of incorporating design for active repair [66]. Essentially, once a fault masking strategy has been determined it may be

Fig. 3. Fine-grained passive redundancy principal for electronics. (a) quad transistor structure (b) standard CMOS NAND logic gate (c) equivalent quad redundant NAND design.

applied fairly readily to hierarchical logic designs, whether fine-grained, cell or block level although evaluation of its resulting impact fault rate behaviour and associated reliability still needs to be performed. In [43], Han and Jonker noted that different strategies are likely to be required to address transient and permanent (and defect) related failures since the underlying binomial distribution applied to examine transient upset behaviour is unsuitable for modelling permanent faults, where statistical independence can no longer be assumed. Majority voting may occur as a function of the topology of the functional gate [69], the principle being to eliminate the classical voter logic by a summation of electrical currents at a common node. In this instance RoRa (reliability-oriented place and route) algorithms may be employed to instantiate TMRlike structures and evaluate them using V-Place, a modelbased tool that uses a topology heuristic to assess and recover performance metrics.

Information redundancy is a further long-established approach distinguished by the fact that errors are allowed to occur and must be corrected. Although mainly as active mitigation there exists hardware designs that exploit this approach when errors can be tolerated. For example, computing in the presence of noise caused by SEUs can be achieved when the numerical error created by an upset does not impinge upon the accuracy of the output [77].

#### B. Active methods

In contrast to fault-masking redundancy methods, fault detection and reconfiguration aim to achieve fault tolerance via BISR capability. Sometimes this is referred to as built-in self-test and repair (BISTAR), the result of combining BIT and BIST. The contrasting behaviour of active and passive strategies is exemplified by revising Fig.1 where, for active strategies, redundant resources are called upon (and consumed) by rising fault severity. By contrast, passive strategies possess much more limited fault capacity in the form of redundant resource but offer fast recovery. Active methods are armed with sufficient resources to maintain a consistently higher fault capacity but with longer recovery times after each fault event. In the ideal case a combined strategy would only address transient faults by the masking method and permanent faults by the active method.

BISTAR initiates a direct response to an upset event in the form of active alteration of the functional logic (and possibly additional dormant logic). BISTAR is fundamentally different to passive mitigation in that a measured response is taken by reorganising internal resources. The variety of active mitigation methods is summarised in Table X. Reorganisation usually involves a process of fault detection and localisation (possibly automated but most likely manual) followed by replacement of faulty logic with logic that is assumed to be fully functional. An example partial reconfiguration of an FPGA by user-initiated loading of a new bitstream after detecting a problem is suspected. This type of maintenance assistance can be highly sophisticated however it does not constitute self-repair. Self-diagnosis should also be qualified here: many circuits contain BIT hardware that is designed to enhance the fault detection process, however these mostly require external test hardware to be connected in order to achieve diagnosis capability [78].

Built-in test (BIT) logic was originally created for production test and repair but lacks the detection capability proposed for online mitigation [79]. This approach has been refined over the years to improve the efficiency of production test, including the introduction of self-repair logic in memory chips. For example, redundant row and column cells for more efficient repair [80] is essentially a more straightforward reallocation process whereby resources are reorganised to circumvent defects. Once processed by the production tester, the configuration remains locked for the remaining lifetime of the component. The envisaged diagnostic, resource and response performance/cost trade-offs were considered in Table VIII and clearly the incorporation of self-repairing capabilities needs additional resources beyond those envisaged for the production test and repair. An example of this is seen in adaptive cache design where a variable trade-off is implemented in hardware [81].

1) Detection and classification: Detection in electronic sub-systems can occur online, during the active operation with minimal service interruption or offline, performed when the system is placed in a special diagnostic mode or else during power on self-test. Present-day detection is typically implemented using some form of boundary scan logic that is made available during offline test. In complex systems this is usually performed during regular or emergency maintenance and inspection. Offline detection is commonplace in production test and repair during which dedicated logic is activated to facilitate the test and repair process [35]. Notably however,

TABLE 9

BOTTOM-LEVEL DESIGN METHODOLOGIES FOR ELECTRONICS

| Method                                      | Example    | Mechanism(s)                                                                                                                                                                             |

|---------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Quad-structures                             | [70], [71] | Quad transistors arranged in serial/parallel fault tolerance. Output is formed from majority of pull up/down resistor current.                                                           |

| N2-transistor structures                    | [72]       | Massively-redundant micro-architectures; variant of quad structures.                                                                                                                     |

| Triple transistor structures for CMOS logic | [73]       | Triple transistor redundancy scheme for minimal area overhead.                                                                                                                           |

| Yield enhancement for next-gen electronics  | [74], [75] | Redundant transistors designed to be allocated only during production test                                                                                                               |

| Interleaved logic and interconnect          | [60]       | Send multiple copies of logic levels to redundant gates so that output is calculated several times. This provides majority output and can be arranged to inherently mask certain faults. |

| Multiplexed redundancy                      | [43]       | Redundancy via additional interconnections                                                                                                                                               |

| FPGA configuration                          | [76]       | Provisioning additional resources ar programmable block level                                                                                                                            |

TABLE 10

ACTIVE MITIGATION STRATEGIES

| Method                           | State of the art                                                                                         | Example                                                                                           |

|----------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Offline test and repair (BISTAR) | Resources organised during test mode. Valid for chip, package and SoC level test & diagnostics.          | [15], [44], [35]                                                                                  |

| Fine-grained reallocation        | Transistor-level reorganisation using switch-over.                                                       | [82]                                                                                              |

| Online test and repair           | Fault & mitigation for critical sub-systems that must not be interrupted; integrated self-test & repair. | Autonomous fault management; ECSS F3 on-board fault management [83]                               |

| Error mitigation                 | Errors permitted to occur then corrected at data level                                                   | [48], [84]                                                                                        |

| Self-healing                     | Autonomic reorganisation, possibly without explicit detection;                                           | FLASH memory recovery, self-healing materials; interconnect possible but very low TRL. [85], [86] |

complexity is retained within production test units that are only available during production. Extensions have been proposed that increase the on-chip complexity in lieu of faster overall test procedures [87]. Beyond production BIT and BIST, the principles of detection lies within the wider research area of anomaly detection [88]. For example, at higher system levels cluster analysis is a powerful data-driven approach for systemlevel health monitoring and diagnostic [89]. However, in the context of this paper it is assumed that detection logic is needed much closer to the point of origin of faults, requiring a step-change in design and integration practices. The goal has become to ensure that errors are not permitted to manifest within electronic logic, interconnections and memory. Fault discrimination is a critical augmentation of detection and opportunities exist within microelectronics design to integrate detection and discrimination close to the point of fault, including assessment of the seriousness of fault. This is made all the more important given detection is the first step towards all active mitigation strategies. In contrast, masking approaches do not depend upon online fault detection, but instead majority

signals are produced that, in turn, generate signals that reflect the current integrity in the presence of threats. Logging and reporting of fault events is clearly a further desirable feature within the general maintenance model, however detection and counting of transient upsets is not trivial. Active mitigation is however very well-suited to status monitoring even before active recovery is considered.

There are examples when fault detection is not used but instead the masking strategy is primed to initiate a default response should particular error occur. Examples include switch-over [36], RAID data storage and error detection and correction (EDC) codes. EDC operates by exploring redundancy applied at the information level by data coding. This differs from hardware mitigation since errors are allowed to manifest and are then corrected. In contrast, hardware methods seek to prevent errors from arising when faults occur. EDC is however extremely popular in memory ICs due to regular architecture of memory cells that allows direct application of data codes. An abstraction between hardware and EDC strategies is sometimes apparent for example, in the protection

of configuration bitstreams for FPGAs. In this case EDC is used to protect data patterns that are in turn responsible for hardware configuration [9]. However the respective detection strategies are still distinct. A further example is when EDC applied to protect look up tables (LUT) that in turn implement finite state machines (FSM). Whereas the FSM is traditionally implemented as a combination of LUT data and execution logic, it is possible in some cases to implement the FSM almost entirely out of memory and therefore EDC becomes the predominant detection mechanism. Alternatively, fault tolerance may be encoded at the state level [90]. Once again, errors are allowed to occur and exist until repaired by the EDC strategy. A further variation of this case is when the FSM is provisioned with both hardware fault mitigation and EDC, thus protecting against different fault mechanisms [84]. Detection also appears in the context of self-healing technologies [22] where autonomic responses are triggered upon certain events. In Table XI a summary of fault detection strategies related mostly to modular designs is presented.

Fine-grained built-in test (BIT) strategies represent an important step towards zero-maintenance capability in electronic sub-systems because they require that faulty conditions are identified and localised before the response is formulated. Another case is that of remotely activated BIST using the System JTAG (SJTAG) method [91] wherein the test itself is offline but is activated by a remote data centre. By comparison, online detection is still in its relative infancy but will bring the facility to identify faults during normal operation with minimal impact on overall performance. Zero-maintenance requires considerably more complex design effort to gather useful information to inform the recovery process. One future strategy is to make extensive use of hardware fault detection at the lowest design levels in conjunction with fine-grained redundant design with new BIT logic [92]. This marks a departure from the reliance upon traditional external test units and a step towards online BIST.

Chip- and board-level system considerations are also important, especially the integrity of interconnects. This is an especially challenging area that has been considered as part of the boundary scan approach [45]. There has been limited progress in this area although IEEE standard 1149.1 has evolved to cater for multi-chip modules (MCMs) [93], on-chip test and even hardware emulation and debug. Analogue time-domain refractometry (TDR) approaches have also been proposed to improve fault coverage and retain low MCM complexity [94]. In most cases online operation is not considered and hence the addition of field support phase capability has been discussed with respect to modified boundary scan hardware [44] and could potentially be applied at the board or system levels. This would essentially constitute an automated approach to circumvention of localised board issues. Beyond this however, there is a great need for further work in interconnect-level fault detection they represent critical points of failure and methods are confined to production test [95].

2) Self-reconfiguration: Off-the-shelf FPGA devices contain reconfiguration logic coordinated by user-provided configuration bitstream that has been generated by software design tools and is typically fixed at design-time. These devices have

become highly popular and have been identified as critical to system dependability in many applications [96]. At the same time, SoC platforms such as the Zync and Cyclone SoC include integrated processors for runtime reconfiguration of programmable FPGA resources including logic, LUTs, memory and interconnects. The principle of reconfiguring resources within an FPGA in response to faults is discussed in [97], noting that the configuration fabric itself remains fixed. Resource utilisation in such cases rarely approaches 100% and therefore unused memory blocks, look up tables, logic resources are available even within complex designs. The challenge associated reconfiguration however lies in effective detection, coordination and resource coverage within the detection strategy. Since access to available resources tend to be clustered with limited granularity, coverage must be carefully managed otherwise available resources may not be accessible.

An external governing process is usually needed that operates online or offline depending on the implementation. This process may take one of two forms: alternative pre-verified bitstreams stored externally and loaded into the device [98] or direct manipulation of the live bitstream by an internal or external governing process. Embedded or software-defined processors have been proposed as part of this but are considered analogous to external processors in terms of resource usage. Sophisticated algorithms such as the STAR approach [99] attempt to self-manage dynamic resource allocation by quarantining active logic that is under test, with the intention that areas of memory and logic affected by faults are less likely to generate errors.

Besides FPGA chips, reconfiguration is also performed within multi-processor hardware where, again, the underlying logic fabric remains fixed but the resource utilisation is dynamically managed by software techniques depending on fault conditions. Typical examples include load balancing and thermal management as well as modular standby sub-components. Finally, the fault-tolerant properties of neural networks have been investigated by incorporating TMR principles into the network [100]. A summary of key design features expected of reconfigurable computer systems can be found in Table XII.

The most flexible of all active response strategies involves dynamic resource reallocation using a generic pool of resources. Here, the underlying logic fabric itself may be altered and manipulated in response to persistent fault events. Dynamic allocation involves substitution of faulty logic and interconnect with healthy hardware in response to a variety of fault conditions. Successful strategies include heterogeneous architectures arranged as a pool of available resources with multiple fixed logic designs that achieve the same task, but each of which have different fault behaviours, thus providing resilience against systemic failures [101]. Kothe (2006) discusses a method for direct reconfiguration at the fine-grained transistor level [82] where a switching fabric is included at the transistor level. Self-coordination at the logic cell level uses simple trigger-based signals to activate or deactivate each cell. This method is related to bio-inspired cellular arrays, and in particular cellular automata, whose functionality is defined by DNA-like instructions stored by cells organised as a regular array structure. This approach is conceptually attractive due to

TABLE 11

FUNDAMENTAL DETECTION CAPABILITIES FOR ZERO-MAINTENANCE

| Method                                              | Mechanism                                                                                                                                                                                                         |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Checkpointing                                       | Save known good state for potential future roll-back. Usually software implemented.                                                                                                                               |

| Spare module                                        | A duplicate module exists in either online or offline state. This is activated when a problem is detected. Requires fault detection.                                                                              |

| Duplicate & match                                   | Primitive of TMR: perform same operation twice and compare results. Often implemented using design diversity i.e., two different implementations are used to help avoid systemic errors.                          |

| Hardware error<br>detection and<br>correction (EDC) | Generally performed on data to be stored and transmitted.  Redundancy is introduced into the data set itself such that certain errors caused by fault are detected and corrected.                                 |

| Temporal redundancy                                 | Time-sharing of resources in order to generate majority vote.                                                                                                                                                     |

| State machine encoding                              | Protection by inserting of redundant states that indicate error states.                                                                                                                                           |

| Virtual TMR                                         | Uses reconfigurable logic blocks to implement TMR when configured correctly. Implementations can be dynamic.                                                                                                      |

| System-level voting                                 | Abstract levels of majority voting to determine system correctness at high level e.g. software level in computing. Somewhat independent of underlying hardware and does not provide indication of cause of error. |

TABLE 12

FEATURES FOUND IN RECONFIGURABLE SYSTEMS

| Feature                 | Description                                                                                                                                      |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Reprogrammable          | Configuration by bitstream or machine code, which can be updated and reloaded.                                                                   |

| Configuration means     | Access to configuration bitstream (FPGAs) or instruction memory (processors)                                                                     |

| Regular architecture    | Multiple identical arrays of logic and memory fabric arranged in a regular fashion.                                                              |

| Embedded processors     | Specific to FPGAs: software-defined processor allow complex task management with hardware resource abstraction.                                  |

| Partial reconfiguration | Pre-verified configurations (FPGA) or machine code (processors) primed for fast reconfiguration of select resources without halting active task. |

the relatively simple rule sets that govern global functionality.

Other instances of self-organisation include dynamic reallocation of microprocessors workloads in the event of a failed worker [102] and self-assembly of patterns by convergent cellular automata that are used to coordinate functional logic cells [103]. The latter achieves self-reassembly of the correct configuration even in the event that every cells state is randomised. The Plastic Cellular Architecture (PCA) has also been suggested [104] taking the form of a CA coordination layer together with a reconfigurable functional logic layer called a "reconfigurable plane". Taken together, they form a self-reconfiguring logic mechanism even though self-repair was not the original focus of this work. Evolutionary algorithms may also be applied to drive self-reconfiguration [105] in which the rule sets are dynamically evolved over time. In [106] a self-recovery mechanism based on a diffusion model is demonstrated using a reconfigurable hardware platform. A further approach uses the redundant genetic information observed in prokaryote organisms to create an artificial prokaryote that controls circuit configuration [107].

# V. TOWARDS A DESIGN STRATEGY FOR ZERO-MAINTENANCE

From the above overview, it is clear that a multitude of strategies relating to maintenance exists that should be carefully matched to the application. This section attempts to set out a forward strategy for designing zero-maintenance into electronic sub-systems and components with reference to the literature classified according to the components of zero-maintenance. A summary of applicable methods is set out in Table XIII in terms of passive and active mechanisms.

For the case of transient upset mitigation the resource requirement is likely to be fixed and the degree of overhead is directly linked to expected fault frequency and corresponding fault capacity. Active mitigation strategies are capable of dynamically issuing redundant elements during the course of operation but resource allocation is considerably more complex and must be determined at design-time. Therefore, redundant resources depicted in Fig. 1 will consumed as cumulative permanent faults occur over time.

An example design for mitigation is seen in for control systems and signal processing applications, where it was noted that system performance degradation is traded for enhanced fault-tolerance [25], [108], [109]. This compromise was generalised in Fig. 1 to include redundant resource requirement. As previously discussed, passive strategies mitigate through masking faults without explicit detection and seek to continue in the presence of those faults without error. Active strategies rely instead upon explicit fault detection before taking action to remove faulty logic. Clearly it is important in the latter case to avoid false alarms triggered by transient faults that cannot be effectively handled by an active response. Even when considering the advancements made key questions remain: how is the integrity of redundant resources ensured, should they be trusted? This may merit a self-test of standby resources before their allocation in response to fault events. A related issue is integrity of redundant resource pool monitoring and communication of remaining resources to the upper design levels. Last but not least-how can integrity of checking logic be ensured?

# A. Design Perspectives

High-value industrial systems are synonymous with high recurring maintenance, repair and overhaul effort that increases the overall cost of through-life support [1]. Failures associated with electronic sub-components lead to costly repair activity and down-time, a symptom that is on the increase within electronic components. OEM and system integrators therefore seek new design methods driven within the electronics domain by increasing IC density, shrinking transistor critical dimension, aggressive voltage and frequency scaling and increasingly complex interconnect and packaging.