# **RADAR**

| High-Speed Low-Voltage Line Driver for SerDes Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Michael Rogers (2009)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| https://radar.brookes.ac.uk/radar/items/d7f9d856-ae6d-4eab-bb7d-aa54376560d6/1/                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Note if anything has been removed from thesis: Appendices 1 and 2                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy car be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder(s). The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders. |

| When referring to this work, the full hibliographic details recent be given as follows:                                                                                                                                                                                                                                                                                                                                                                                                                    |

| When referring to this work, the full bibliographic details must be given as follows:                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Rogers, M (2009) High-Speed Low-Voltage Line Driver for SerDes Applications PhD, Oxford Brookes University                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# High-Speed Low-Voltage Line Driver for SerDes Applications

By

Michael Rogers

School of Technology Oxford Brookes

In Collaboration With Texas Instruments

A thesis submitted in partial fulfillment of the requirements of Oxford Brookes University for the degree of Doctor of Philosophy

October 2009

#### **Acknowledgements**

I would like to thank Oxford Brookes and Texas Instruments for providing me with this research opportunity. Without the collaboration between these two organisations this research would have been impossible for me to undertake.

Both Oxford Brookes and Texas Instruments provided me with an outstanding support network providing me with the tools, knowledge and funds needed to carry out this research within the 3 year time frame allotted.

Specifically I would like to thank my primary supervisor Khaled Hayatleh for introducing me into analog circuit design and putting me forward for this research opportunity. Throughout this research program he has always made himself available to me when ever I needed help.

I would also like to thank my second supervisor John Lidgey, his advice and support was crucial throughout this research program.

And from Texas Instruments I would like to thank their UK Design Team for taking me under their wing. Specifically I would like to thank:

- Richard Williams, for ensuring the legal and financial side ran smoothly.

- Mike Harwood, for providing detailed technical help throughout the design process of my novel work.

- Andy Joy, again for providing technical help and advice throughout this research.

- David Sebastio, for teaching me how to use Cadence and providing technical help throughout the design stage of the novel work.

- Terry Ward, for his valuable insight and training he provided me when taking my design to layout.

Finally I would like to thank my family for their support, without their help and advice I would not have made it this far through a very long education route, and I would like to thank my loving girlfriend for putting up with me through the stressful times.

Thank you to everyone involved.

Mike Rogers October 2009

#### **Abstract**

The driving factor behind this research was to design & develop a line driver capable of meeting the demanding specifications of the next generation of SerDes devices. In this thesis various line driver topologies were analysed to identify a topology suited for a high-speed low-voltage operating environment.

This thesis starts of by introducing a relatively new high-speed communication Device called SerDes. SerDes is used in wired chip-to-chip communications and operates by converting a parallel data stream in a serial data stream that can be then transmitted at a higher bit rate, existing SerDes devices operate up to 12.5Gbps. A matching SerDes device at the destination will then convert the serial data stream back into a parallel data stream to be read by the destination ASIC. SerDes typically uses a line driver with a differential output. Using a differential line driver increases the resilience to outside sources of noise and reduces the amount of EM radiation produced by transmission.

The focus of this research is to design and develop a line driver that can operate at 40Gbps and can function with a power supply of less than 1V. This demanding specification was decided to be an accurate representation of future requirements that a line driver in a SerDes device will have to conform to.

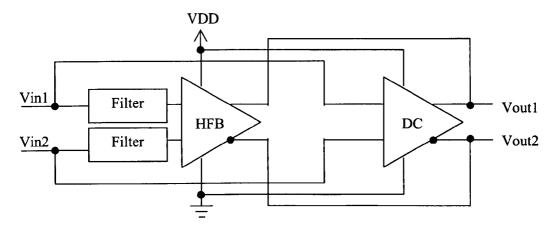

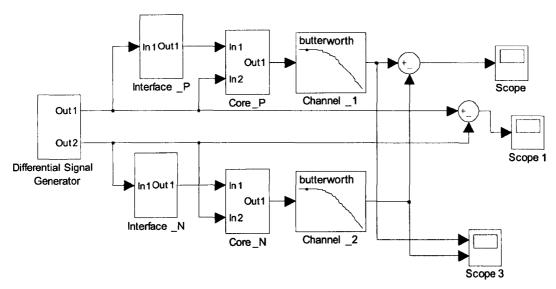

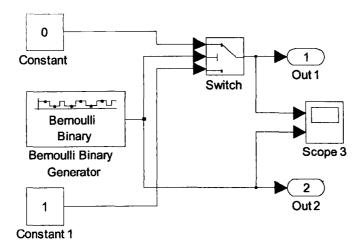

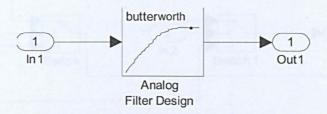

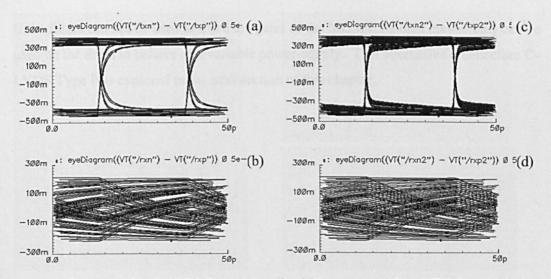

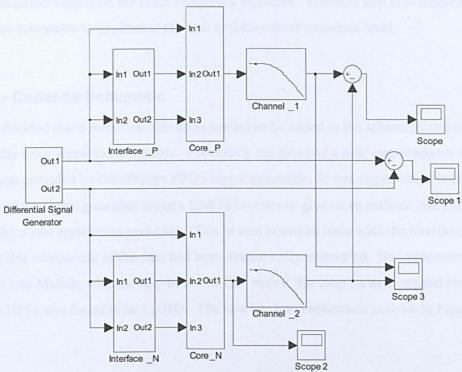

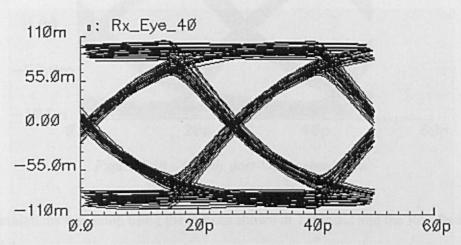

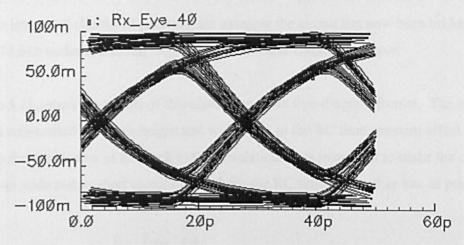

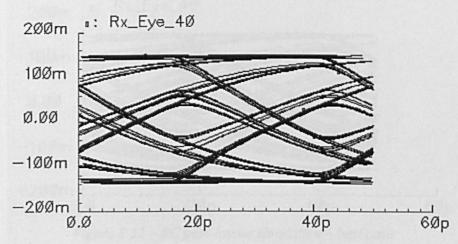

A suitable line driver with a differential output was identified to meet the demanding specifications and was modified so that it can perform an equalisation technique called pre-distortion. Two variations of the new topology were outlined and a behavioural model was created for both using Matlab Simulink. The behavioural model for both variants proved the concept, however only one variant maintained its performance once the designs were implemented at transistor level in Cadence, using a 65nm CMOS technology provided by Texas Instruments.

The final line driver design was then converted into a layout design, again using Cadence, and RC parasitics were extracted to perform a post-layout simulation. The post layout simulation shows that the novel line driver can operate at 40Gbps with a power supply of 1V-0.8V and has a power consumption of 4.54 mW/Gbps. The Deterministic Jitter added by the line driver is 12.9ps.

# List of principal symbols and acronyms

SerDes Serialiser / Deserialiser

ZTC Zero Temperature Coefficient

PCI-E Peripheral Component Interconnect Express

SATA Serial Advanced Technology Attachment

SAS Serially Attached Small Computer System Interface

IC Itegrated Circuit

ASIC Application Specific Integrated Circuit

PLL Phased-locked loop

I/O Input / Output

Gbps Gigabit per Second

Tx Transmitter

Rx Receiver

RC Resistor and Capacitor

ISI Inter-Symbol Interference

TI Texas Instruments

CML Common Mode Logic

LVPECL Low-Voltage Positive Emitter Coupled Logic

LVDS Low-Voltage Differential Signalling

HPF High Pass Filter

PRBS Pseudo-Random Bit Sequence

$G_m$  Transconductance

$g_m$  Transconductance of a CMOS device

Av Voltage gain

$\beta$  Transconductance parameter

$V_T$  Threshold Volatge of a CMOS device.

$V_A$  Early Voltage

$f_{\rm T}$  Transistor unity-gain frequency

$f_{-3dB}$  Closed-loop -3dB frequency

$I_D$  Drain current.

$\lambda$  CMOS transistor channel modulation effect.

$C_{ox}$  Gate oxide capacitance for a CMOS device

$C_{gs}$  Intrinsic Gate-Source capacitance

$C_{gd}$  Intrinsic Gate-Drain capacitance

$C_{db}$  Intrinsic Drain-Body capacitance

r<sub>o</sub> Small-signal output resistance of a CMOS device

m Current mirror transfer ratio

CMOS Complementary Metal Oxide Silicon.

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

THD Total Harmonic Distortion

TIA Transimpedance Amplifier

#### **Contents**

| Acknowledgement                                       | i    |

|-------------------------------------------------------|------|

| Abstract                                              |      |

| List of Principal Symbols                             | iii  |

|                                                       |      |

| Chapter 1 – Introduction                              |      |

| 1.1 Motivation for Thesis                             |      |

| 1.2 Main Objectives                                   |      |

| 1.3 Thesis Outline and Structure                      | 1-4  |

| 1.4 Original Work                                     | 1-7  |

| 1.5 References                                        | 1-7  |

| Chapter 2 – Overview of Serialiser Deserialiser       | 2-1  |

| 2.1 Introduction                                      |      |

| 2.1.1 SerDes Architecture.                            |      |

|                                                       |      |

| 2.1.2 Challenges facing SerDes.                       |      |

| 2.2 Role of the Line Driver in SerDes                 |      |

| 2.2.1 Introduction.                                   |      |

| 2.2.2 Differential Signaling.                         |      |

| 2.2.3 Noise                                           |      |

| 2.2.4 Channel Characteristics and Equalisation        |      |

| 2.3 References                                        | 2-17 |

|                                                       |      |

| Chapter 3 – Critical Review of Line Driver Topologies |      |

| 3.1 Introduction                                      |      |

| 3.2 Device Parameters                                 |      |

| 3.3 Current Mode Logic                                | 3-9  |

| 3.4 Low Voltage Positive Emitter Coupled Logic        | 3-22 |

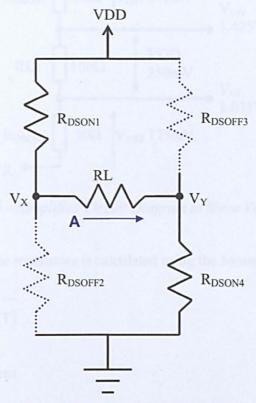

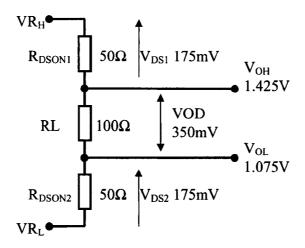

| 3.5 H-Bridge                                          |      |

| 3.6 Low Voltage Differential Signalling               |      |

| 3.7 Conclusion                                        |      |

| 3.8 References                                        |      |

|                                                       |      |

| Chapter 4 – Composite LVDS                            | 4-1  |

| 4.1 – Introduction                                    | 4-2  |

| 4.2 – Concept                                         | 4-2  |

| 4.3 - Design procedure                                |      |

| 4.4 – C-LVDS Type A                                   |      |

| 4.4.1 - Behavioural Model                             |      |

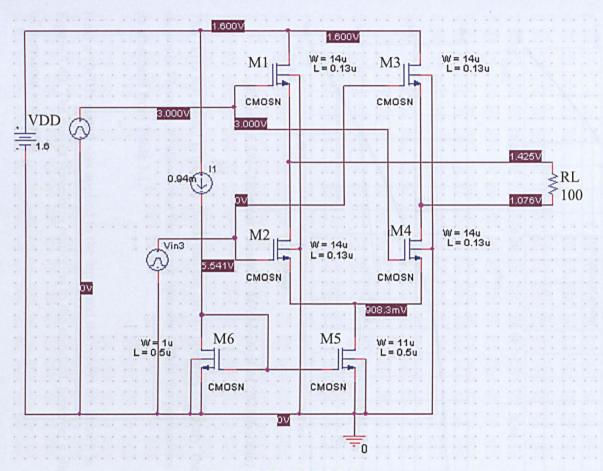

| 4.4.2 - Cadence Schematic.                            |      |

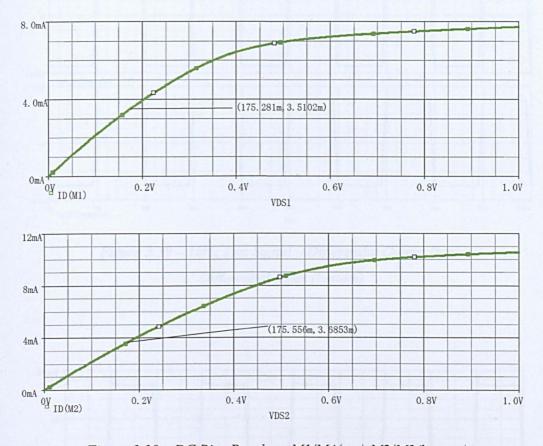

| 4.4.3 - Simulation Results                            |      |

| 4.4.4 – Conclusion.                                   |      |

| 4.5 – C-LVDS Type B                                   |      |

| 4.5.1 - Behavioural Model.                            |      |

|                                                       |      |

| 4.5.2 - Cadence Schematic                             |      |

| 4.7.3 - Simulation Results                            | 4-73 |

| 4.6 – Summary and Conclusions.44.7 – References.4     |       |

|-------------------------------------------------------|-------|

| Chapter 5 – Layout and Post-Layout Simulation         | .5-1  |

| 5.1 - Introduction                                    |       |

| 5.2 – Photolithography                                |       |

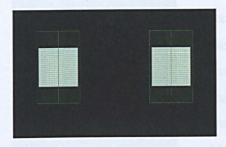

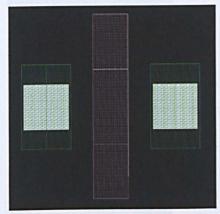

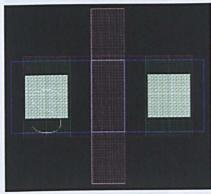

| 5.3 - Layout Floor plan & Mask Design                 |       |

| 5.3.1 – Floor Plan                                    |       |

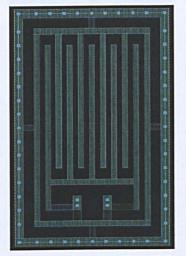

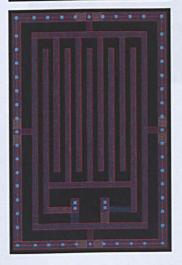

| 5.3.2 – Mask Design: DC Driver                        |       |

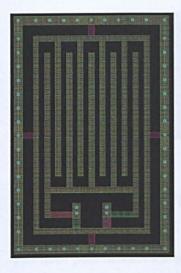

| 5.3.3 – Mask Design: HF Booster                       |       |

| 5.3.4 – Mask Design: 10GHz Filter                     |       |

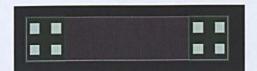

| 5.3.5 – Mask Design: Interface                        |       |

| 5.3.6 – Mask Design: Top Level                        |       |

| 5.4 - Post Layout Simulation                          |       |

| 5.4.1 – Ideal                                         |       |

| 5.4.2 – C Only                                        |       |

| 5.4.3 – RC Best Corner                                |       |

| 5.4.4 – RC Worst Corner                               |       |

| 5.5 – Discussion                                      |       |

| 5.6 - References                                      |       |

|                                                       |       |

| Chapter 6 – Conclusions, Future work and Applications | .6-1  |

| 6.1 – Conclusions                                     | 6-2   |

| 6.2 – Future Work                                     | 6-8   |

| 6.3 – Applications                                    | . 6-9 |

| 6.4 – References                                      | 5-10  |

| Reference List.                                       | .7-1  |

|                                                       |       |

| Appendix 1                                            | .8-1  |

| Appendix 2                                            | .9-1  |

# Chapter 1

# Introduction

| 1.1 Motivation for Thesis        | 2 |

|----------------------------------|---|

| 1.2 Main Objectives              |   |

| 1.3 Thesis Outline and Structure |   |

| 1.4 Original Work                |   |

| 1.5 References                   |   |

#### 1.1 Motivation for Thesis

The conventional method of conveying electronic data at high data rates is to use parallel rather than serial transmission [1]. However, as the data rates continue to increase into the gigabit range, parallel transmission becomes problematic due to multi-path synchronisation difficulties as well as being expensive to implement [2]. The industry is resolving the problem by introducing high-speed serial technology. For example there are several different industry standards, including PCI-E (Peripheral Component Interconnect Express), SATA (Serial Advanced Technology Attachment), and SAS (Serially Attached Small Computer System Interface) which are all inter-computer serial communication protocols that have been developed from parallel predecessors [1,3].

A circuit that is used to convert parallel data to serial data for serial data transmission and then receive the serial data and convert it back to parallel data is referred to as a Serialiser / Deserialiser, which is abbreviated to SerDes [4,5]. It can either be a stand-alone device or integrated into an Application Specific Integrated Circuit (ASIC). Its function is to convert the input parallel data stream into an output serial data stream for transmission. On the receiver end a SerDes is used to reconvert the incoming serial data stream back into parallel output data. The further features included in a SerDes device are clock recovery/generation for synchronisation, channel equalisation, error correction and data encoding [6].

SerDes can be found in wireless routers[4], fibre optic communication systems, mobile phones and base stations, super computers[7], liquid crystal displays, anywhere that a high speed link is needed with very low data errors[8]. For example super computers are given mammoth tasks to accurately predict global weather and climate change[2] which involves large amounts of data to be transmitted between processor clusters at high speeds with low error rates. SerDes is used to allow the clusters of processors to communicate at data rates up to 10Gb/s with bit error rates of 10<sup>-12</sup> [3,4,9].

The bit error rate (BER) of  $10^{-12}$  was chosen as it is stated in the IEEE 802.3 standard [10]. This value was chosen by the 802.3 standard as a target BER because it was measurable. However as data rates increased the minimum measurable BER also decreased and today a BER of  $10^{-15}$  is measurable.

This research program is sponsored by Texas Instruments, (TI), and the work is focused on the development of high speed inter-computer communication electronics. This is a particular strength of TI with their UK Design Centre at Northampton being responsible for these circuit and system developments. The likely destination for the results of this research will be for high speed communication links between processors within a super-computer.

The primary aims of this thesis are to i) critically review and investigate the challenges facing SerDes as speeds reach 40Gbps while maintaining the bit error rate of  $10^{-12}$ , ii) design and develop a novel transmitter to help overcome the challenges of high speed communications. Key parameters such as chip area, power consumption, and maximum speed will be used as figures of merit for comparison purposes in evaluation of different designs.

# 1.2 Main Objectives

There are many aspects to SerDes design including the transmitter, receiver, phased-locked loop (PLL) and mixed signal routing. Each comes with its own challenges and a design team of experts is required to overcome them. Due to the complexity of high speed data transmission I will be focusing my efforts on the transmitter, which in the case of SerDes is called a 'line driver'.

The main objective of this research is to design a novel line driver to meet the "future proof" specification of:

- A supply rail (VDD) of 1V

- Operating frequency = 40Gbps

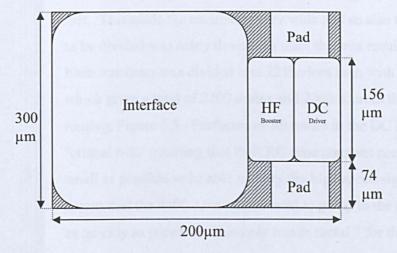

- Chip area =  $200\mu\text{m}^2$ , which is defined by the area available for the line driver on a test chip supplied by Texas Instruments.

- Transistor technology = CMOS 65nm, which can be readily migrated to smaller geometry processes.

Due to deep sub-micron technology devices and power consumption requirements the rail voltage of 1V is becoming more and more prevalent. Furthermore, due to power distribution losses on the die, the rail voltage can be as low as 0.85V by the time it reaches the transmitter.

The typical challenges of high speed data transmission will be identified and a range of relevant techniques will be reviewed that have been developed to address these challenges.

To achieve these demanding specifications a detailed study of existing line driver topologies will be undertaken to identify which design techniques can be applied to the high-speed low-voltage environment.

# 1.3 Thesis Outline and Structure

This thesis is seven chapters in total. Following this introductory chapter, Chapter 2 introduces the concept of the SerDes device including why it is needed for high speed data transmission and operating principles. Also in Chapter 2 the line driver and its role within SerDes is examined in detail.

In Chapter 3 the performance of four existing different driver topologies are critically reviewed and compared with the aim of identifying which type would fit the tight performance specifications (1.2 above) that the novel driver has to achieve. In addition Chapter 3 also contains the device parameters of all transistors used in this research. Having completed the ground work discussed in Chapter 3, a driver topology suitable for low-power high-speed transmission has been identified along with its strengths and weaknesses.

The thesis contains two MOSFETs from different companies. The more advanced of the two is the Texas Instruments 65nm "model". This 65nm model is specifically for low voltage circuits where a typical power supply is 1V. This transistor will be used in the novel Chapters of this thesis where supply voltages will be 0.8V - 1V. At 2V the gate oxide breaks down thus a second transistor with a thicker gate oxide is needed for the high voltage applications, i.e. applications with supply voltages greater than 2V.

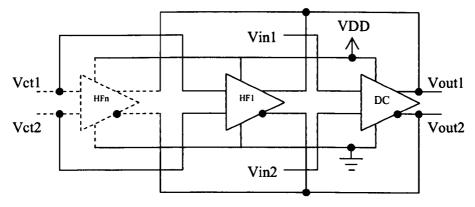

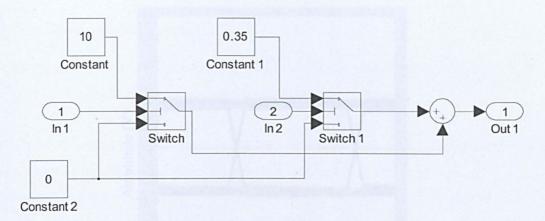

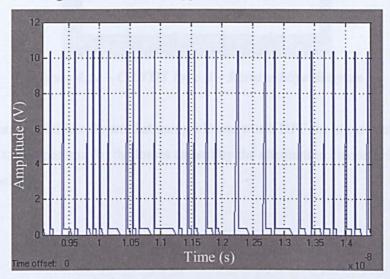

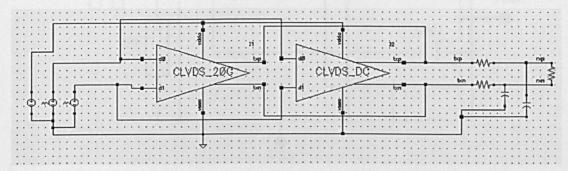

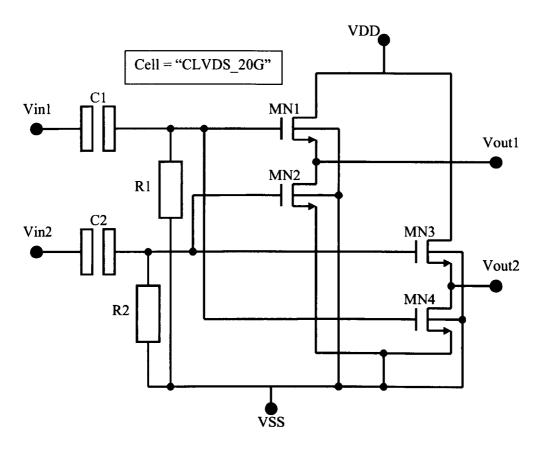

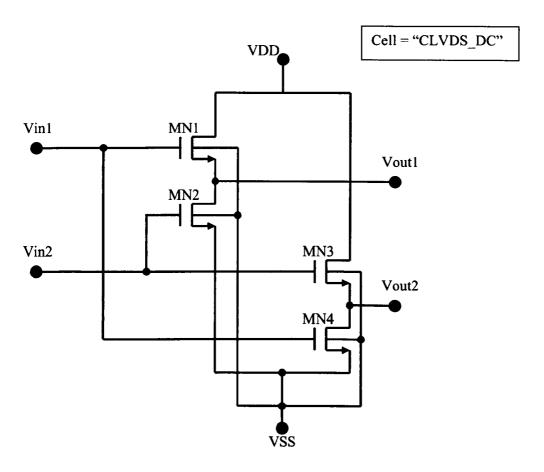

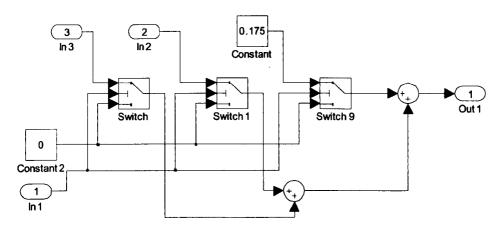

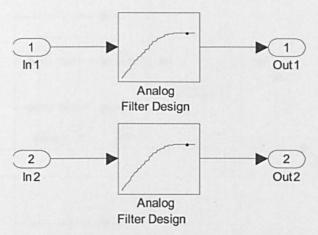

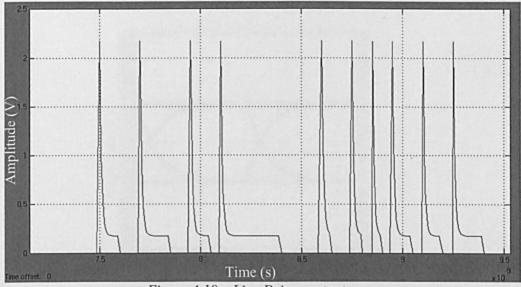

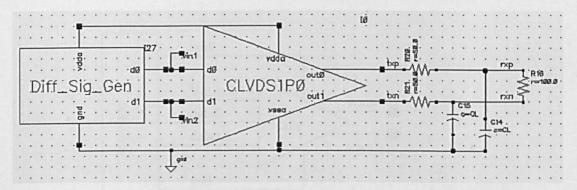

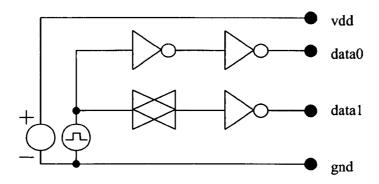

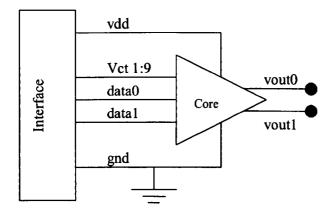

The second model to be used is the IBM T68A 130nm MOSFET. This transistor will be used in the critical review chapter where higher supply voltages are used to meet the standards specifications. The focus of Chapter 4 is on the design and development of a novel SerDes line driver. Using an adapted Low-Voltage-Differential Signaling (commonly referred to as LVDS) architecture I have designed a novel line driver, named Composite-LVDS (C-LVDS), which can adjust its gain depending on the frequency of the input data, performing a form of equalisation on the transmitter end. Two versions of C-LVDS are presented and verified mathematically in a behavioral model designed in Matlab before the transistor level model is designed in Cadence. Also in Chapter 4, different ways in which the driver can detect its operating frequency are identified, and then used to adjust the transmitter gain.

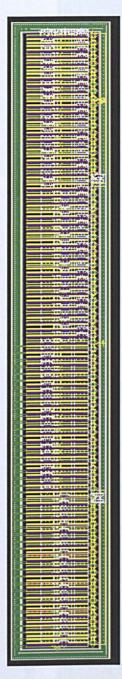

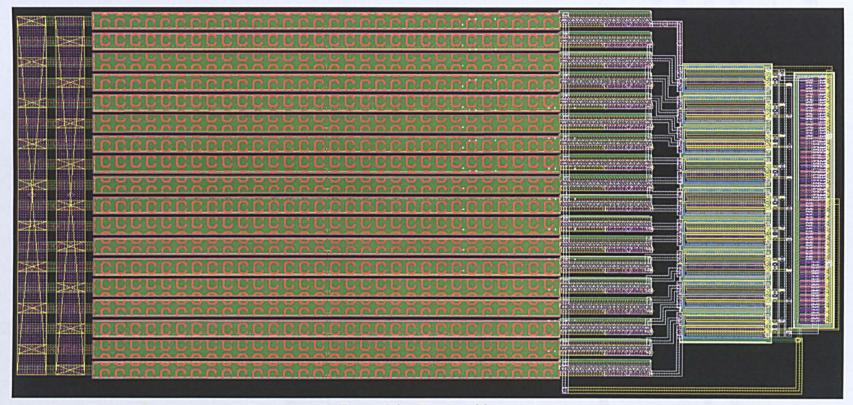

The layout floor-plan will be presented in Chapter 5 and will provide all the rules and layout techniques used to achieve this level of performance. Chapter 5 also contains one of the most important and realistic simulations possible in Cadence, called a RC Post-Layout simulation. This simulation contains all the parasitic resistances and capacitances, hence the term 'RC', which will be added by the metal traces used in the routing of the devices.

Finally Chapter 6 will wrap up the thesis with any conclusions that can be drawn about the novel line driver, C-LVDS, as well as any future work to be carried out.

### 1.4 Original Work

There have been several areas of original work throughout this thesis, a summary is shown below:

• In Chapter 2 I investigated the use of a device called SerDes. Typical noise factors are described and analysed. Common types of channel equalisation are also investigated.

- In Chapter 3 I investigated various line driver topologies. I characterised two geometries of CMOS MOSFETs, 130nm and 65nm, which were then analysed to ensure performance at 40Gbps and various levels of VDD.

- In Chapter 3 I critically analyse four popular line driver topologies:

- 1. Common Mode Logic (CML).

- 2. Low-Voltage Positive Emitter Coupled Logic (LVPECL).

- 3. H-Bridge.

- 4. Low-Voltage Differential Signaling (LVDS).

- In Chapter 4 I investigated how channel equalisation can improve performance at 40Gbps. My novel line driver topology is introduced as Composite-LVDS (C-LVDS) which comprises of LVDS style drivers employing a pre-distortion channel equalisation technique, two further variants of C-LVDS are designed and the high speed performance of both circuits is analysed in this chapter.

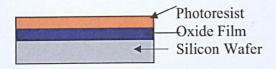

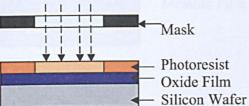

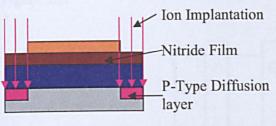

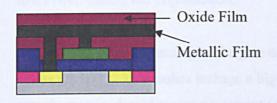

- In Chapter 5 I continue the development of C-LVDS by designing a mask set for use in Photolithography.

- Chapter 5 continues with a Monte Carlo analysis that I performed on the final design of my novel line driver with the added parasitics that I extracted from the layout.

- Chapter 6 concludes the thesis with a discussion of the final design of my novel line driver. I

discuss future work and possible applications of C-LVDS.

Two Papers have been produced from this research. The first paper, found in Appendix 1, contains preliminary results and findings and was published in the Analog Signal Processing Conference Proceedings in 2008. The second paper, found in Appendix 2, contains full results and findings and has been submitted to the ISCAS 2010 Conference.

#### 1.5 References

- [1] G. Riley, 'Design High-Speed Data Links With Link-Level Simulation', ED Online, http://electronicdesign.com/article/communications/page/1/design-high-speed-data-links-with-link-level-simul.aspx, accessed December 2007.

- [2] G.C. Williams, 'Trends in Extremely High Speed Data Transfer and the Challenges they Present', ASP2006 Conference Proceedings, Nov 2006.

- [3] J.C. Chen, 'Multi-Gigabit SerDes: The Cornerstone of High Speed Serial Interconnects', Genesys Logic America, Inc., 2003.

- [4] T. Beukema, et al, 'A 6.4-Gb/s CMOS SerDes Core With Feed-Forward and Decision-Feedback Equalization', IEEE Journal of Solid State Circuits Vol 40, December 2005, pp.2633-2645.

- [5] K. Iniewski, et al, 'SERDES technology for gigabit I/O communications in storage area networking', System-on-Chip for Real-Time Applications, 2004 Proceedings, 4th IEEE International Workshop, 2004, pp.247- 252.

- [6] D. Lewis, 'SerDes Architectures and Applications', National Semiconductor Corporation, http://www.national.com/appinfo/lvds/files/designcon2004\_serdes.pdf, accessed November 2006.

- [7] M. Harwood, et al, 'A 12.5Gb/s SerDes in 65nm CMOS Using a Baud-Rate ADC with Digital Receiver Equalization and Clock Recovery', 2007 IEEE International Solid-State Circuits Conference, Vol. 24.1, 2007, pp. 436 437.

- [8] E.H. Suckow, 'Basics of High-Performance SerDes Design, Part I & II', http://www.analogzone.com/iot\_0414.pdf, accessed January 2007.

- [9] M. Ishida, et al, "A Method for Testing Jitter Tolerance of SerDes Receivers Using Random Jitter," in Proc. Int. Engr. Consortium DesignCon 2007, January 2007.

# Chapter 2

# **Overview of Serialiser Deserialiser**

| 2.1 Introduction                               | 2  |

|------------------------------------------------|----|

| 2.1.1 SerDes Architecture                      | 2  |

| 2.1.2 Challenges facing SerDes                 | 4  |

| 2.2 Role of the Line Driver in SerDes          | 8  |

| 2.2.1 Introduction                             | 8  |

| 2.2.2 Differential Signaling                   | 8  |

| 2.2.3 Noise                                    |    |

| 2.2.4 Channel Characteristics and Equalisation | 13 |

| 2.3 References                                 |    |

#### 2.1 Introduction

SerDes stands for Serialiser / Deserialiser and is a relatively new device for converting parallel links into high speed serial links. SerDes is an I/O interface to be added between two devices using a parallel data stream, where its job would be to convert the parallel data stream into a serial data stream and back to parallel at the other side of the channel, shown in Figure 2.1. SerDes can be a separate device, or it can be integrated directly into the Application Specific Integrated Circuit (ASIC) replacing the conventional parallel I/O device[1]. This integrated solution had a profound effect on the SerDes device as it has made it possible to move a lot of the digital architecture involved into the ASIC.

This parallel to serial conversion is important as for a given number of links the data that can be transferred between chips goes up from 1Gbps/link to 10Gbps/link and reduces the link count by a factor of 10, or alternatively allows ten times as much data to be transferred between chips. The typical data transfer rate of a super computer is in the Tb/s region, therefore 100 10Gb/s links are needed for each Tb.

# 2.1.1 SerDes SerDes Channel Serialiser A S I C DeSerialiser DeSerialiser

Figure 2.1 – SerDes Overview [1]

Figure 2.1 shows that the ASIC transmits and receives a parallel data stream. However the data is transmitted over a transmission line in a serial manner.

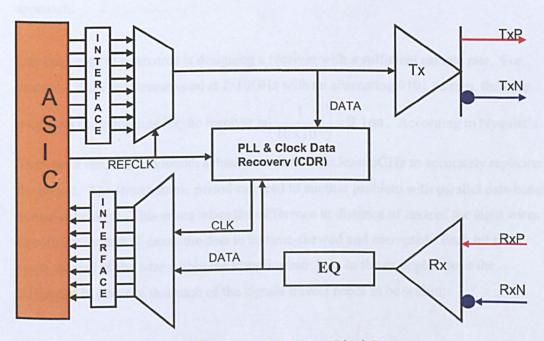

A simplified block diagram of the SerDes architecture is shown in Figure 2.2, which was adapted from [1,2,3]. Starting on the left of the diagram is the ASIC which is the device that is sending and receiving the data, usually to another ASIC. This data is intercepted by the SerDes device using a sample and hold latch, commonly referred to a D-Type flip-flop.

The latch can be used to redefine signal voltage levels for use by the multiplexer. A clock signal (REFCLK) is provided by the ASIC to be used for the timing of the multiplexer. The multiplexer converts the parallel data into a serial data stream, but before the signal is transmitted a clock signal needs to be added to the data for synchronisation of the receiver. The clock signal is derived by using a PLL to multiply the REFCLK signal provided by the ASIC.

Figure 2.2 - Simplified SerDes Block Diagram

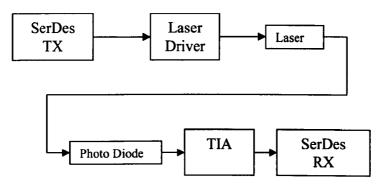

Once the clock signal has been added to the data it is transmitted using a line driver which uses the differential signalling method, indicated by TxP and TxN.

SerDes has the ability for full duplex transmission as it also contains a receiver, which receives the differential signal using a differential receiver. An equalizer (EQ) is used to equalize the signal to improve Bit Error Rate (BER)[2]. The synchronization clock is extracted from the data using a Clock and Data Recovery (CDR) circuit which provides the clock for the de-multiplexer. Finally the data is run through a latch to redefine the voltage levels for the ASIC.

#### 2.1.2 Challenges facing SerDes

Converting data from parallel to serial for high speed transmission may seem counter intuitive as for many years parallel has always been seen as the faster method of sending data. Although this is still true at low frequency transmission, to achieve data rates in the gigabit range the introduction of SerDes provides a cost effective and practical alternative approach.

One challenge to overcome is designing a receiver with a sufficient sample rate. For example, if the data transmitted at f=10GHz with an alternating 0101 pattern, then the minimum sampling rate for the receiver is  $\left(\frac{1}{10\times10^9}\right)$  = 0.1ns. According to Nyquist's

Theorem a receiver bandwidth actually needs to be at least 5GHz to accurately replicate the output. The short sample period can lead to another problem with parallel data buses named data skew. This arises when the difference in distance of each of the eight wires is significant enough to cause the data to be time-skewed and corrupted. Each bit must reach the end of the wire within the sampling rate [1]. In the example above the difference in distance that each of the signals travels needs to be within:

$$v_{o} = \frac{1}{\sqrt{\omega_{o}\varepsilon_{o}}}$$

where:

$$v_{o} = \text{velocity of an electron in freespace.}$$

$$v_{(line)} = \frac{1}{\sqrt{\omega_{o}\varepsilon_{r}\varepsilon_{o}}} = \frac{v_{o}}{\sqrt{\varepsilon_{r}}}$$

$\varepsilon_{o} = \text{vacuum permittivity}$

$$for \varepsilon_{r} = 4$$

$\varepsilon_{r} = \text{relative permittivity}$

$$v_{(line)} = \frac{v_{o}}{2}$$

$\omega_{o} = \text{resonance frequency}$

$$v_{o} = c = 3_{\times 10}^{8} \, \text{m/s} = 30 \, \text{cm/ns}$$

$$v_{(line)} = \frac{v_{o}}{2} = 15 \, \text{cm/ns}$$

Assuming the receiver has a 5% tolerance to skew then the time maximum time variance tolerance becomes 5% of the period = 0.005ns.

$$\therefore \Delta l = \frac{v_o}{2} \times 0.005 ns$$

$$= \underline{0.75 mm}$$

By using serial transmission architecture the data skew problem is greatly reduced as only two wires in a differential pair need to be matched and the cost of the system is reduced as less pins/wires/traces are needed for transmission.

Another problem faced by SerDes devices operating at high speeds is signal degradation due to the bandwidth limitation of the channel's electrical properties, the skin effect and dielectric loss, at high frequencies[4].

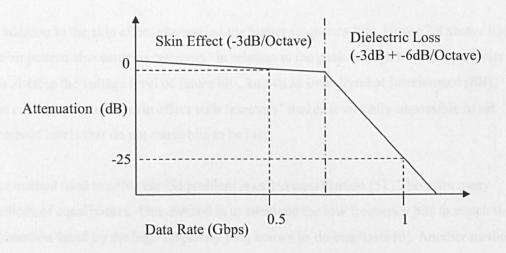

The problem of the skin effect arises due to the nature of the transmission lines attenuation properties in relation to speed. Consider the bit pattern 1010110011. The first four bits represent the maximum bit rate while the final six bits will appear as half the maximum frequency. An example transmission line bandwidth is shown in Figure 2.3. In this case the maximum bit rate is 1Gbps, this means the last six bits will have an effective data rate of 0.5Gbps. According to Figure 2.3 the attenuation for the first part of the data is greater than the second, and the through delay also varies.

Figure 2.3 – Example attenuation characteristics of a theoretical transmission line

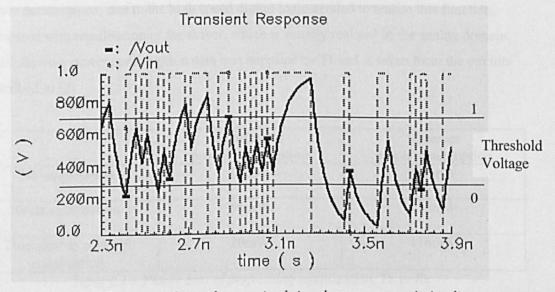

The input and output waveforms can be compared to see how the skin effect and dielectric loss alters the transmitted signal, as shown in Figure 2.4 which was obtained through Cadence using a Pseudo-Random Bit Sequence (PRBS) generator driving a single pole RC filter. It can be clearly seen that the high frequency bits have been greatly attenuated compared with the low frequency bits and no longer reach the threshold levels of the receiver.

Figure 2.4 - Transmitted signal vs received signal over a transmission line

In addition to the skin effect attenuating the higher frequency bits, Figure 2.4 shows how the bit pattern also contains 'memory' in relation to the peak voltage levels of previous bits altering the voltage level of future bits, known as Inter-Symbol Interference (ISI). The combination of the skin effect with 'memory' makes it virtually impossible to set threshold levels that do not cause bits to be lost.

The method used to solve the ISI problem is called equalization [5]. There are many methods of equalisation. One method is to attenuate the low frequency bits to match the attenuation faced by the high frequency bits, known as de-emphasis [6]. Another method would be to boost the high frequency bits to overcome the attenuation of the channel, known as pre-emphasis [6]. Pre-emphasis and De-emphasis can be performed by the transmitter and are discussed in more detail later in this chapter.

One more method of equalisation is called Decision Feedback Equalisation (DFE) and can only be performed by the receiver [2]. This method works by the receiver looking at n previous bits in the pattern and predicting what the voltage level of the next bit will be. The receiver will then adjust its threshold voltage accordingly. This method is very complex [7] and can only be performed by the receiver making it costly in terms of power consumption, due to the high speed digital logic needed to realise this function, compared with equalisation of the driver, which is usually realised in the analog domain. The following power consumption data was supplied by TI and is taken from the circuits described in [2]

|                                    | Transmitter power consumption | Receiver power consumption |

|------------------------------------|-------------------------------|----------------------------|

| No equalisation                    | 36mW                          | 100mW                      |

| With equalisation                  | 56mW                          | 216mW                      |

| Total cost to perform equalisation | 20mW                          | 116mW                      |

Table 2.1 – Power cost of performing equalisation, Tx vs Rx

Clearly from the data in Table 2.1 it can be seen that engineering effort is best concentrated on the transmitter where greater power efficiency can be achieved.

#### 2.2 Role of the Line Driver in SerDes

#### 2.2.1 Introduction

The role of the line driver is to prepare a digital signal for transmission over a transmission line for extended distances and to increase the reliability (BER target 1 x 10<sup>-15</sup>) of transmission of the digital signal. There are many types of line driver architectures that may be considered for this, which will be discussed in Chapter 3. Digital signals are made up of many harmonics to make a square wave, however over long distances and at high speeds the higher harmonic components suffer greater attenuation distorting the signal[8].

The SerDes line driver is essentially an amplifier designed to send the digital signal down a transmission line interconnecting two or more electronic devices together. The primary roles are (i) to condition the signal to compensate for the non-ideal characteristics of the transmission line and (ii) to launch the signal with a low output impedance as closely matched to that of the transmission line as possible.

#### 2.2.2 Differential Signaling

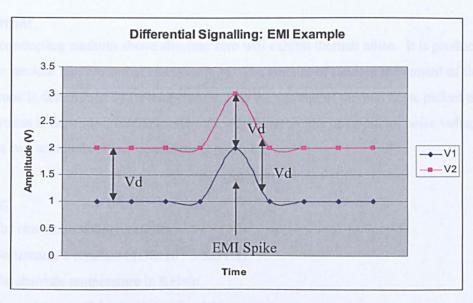

Differential signaling is commonly used in areas that are prone to large amount of common-mode noise, such as mains interference and ground offsets, and car electronic systems like CAN Bus [9]. Differential signaling is set up by using two transmission lines in parallel and in close physical proximity to each other. The data is then sent down both lines by a dual output transmitter where the outputs are in anti-phase [10]. To recover the data the receiver then takes the difference between the two signals and any common-mode interference/noise is cancelled. Figure 2.5 shows how differential signaling can be used to remove noise spikes created by Electro-Magnetic Interference (EMI).

Figure 2.5 - Removing EMI with differential signaling

Although the EMI spike has caused a voltage level increase, both transmission lines were affected equally, therefore the voltage difference (Vd) between them stays the same.

Less EMI is created by the differential signals compared with single ended signal due to the fact that the signals are of opposite polarity, resulting in a cancellation of the magnetic field caused by the electrons flowing through the wire [11].

Another benefit of differential signaling is due to the signal not being referenced to ground, whereas in single ended signaling it is. This means that the transmitter and receiver may operate on different grounds without causing signal level errors [11].

#### **2.2.3** Noise

Three types of noise that are common to transmission systems, due to the nature of active devices [12], namely (i)Thermal (or Johnson-Nyquist noise), (ii) Shot and (iii) 1/f noise (or Pink noise). A fourth noise component common to SerDes in particular is called Jitter [3]. The origins of each type of noise will be discussed below, leading to relevant equations that define them.

#### Thermal

Any conducting medium above absolute zero will exhibit thermal noise. It is produced by the random movements of electrons [13]. The amount of random movement of the electrons is determined by its temperature, also the amount of thermal noise picked up by the system is dependent on the bandwidth, and therefore the open-circuit noise voltage across two terminals of any conductor is given by:

$$V = \sqrt{4kTRB} \tag{2.1}$$

where,

V =the rms noise voltage in volts

$k = Boltzmann's constant (1.38x10^{-23} J/Kelvin)$

T =the absolute temperature in Kelvin

R =the resistance of the conductor in ohms

B =the bandwidth in hertz.

#### **Shot**

Shot noise is produced by the particle like nature of a flow of electrons. As the flow of current is made up of individual electrons there are moments in time where the amount of electrons flowing fluctuates, causing minor changes in the current, which is seen as noise [13]. Shot noise is found using the formula,

$$I_n^2 = 2qI_{dc}B \tag{2.2}$$

where.

$I_n^2$  = the mean square noise current

q =the electron charge (1.6x10<sup>-19</sup>coulombs)

$I_{dc}$  = the direct current in amperes

B =the bandwidth in hertz.

#### 1/f

This type of noise is found in all active devices [12]. Its origins vary but are mainly caused by 'traps' made up from impurities in the silicon where carriers are stored and released at random times.

This type of noise is also known as Flicker noise and is dependent on a flow of direct current. It displays a spectral density in the form of

$$\overline{I^2} = K_1 \frac{I^a}{f^b} \Delta f \tag{2.3}$$

where,

$\Delta f$  = bandwidth at frequency f

I = direct current

$K_1$  = constant for particular device

a = constant in the range 0.5 to 2

b = constant of about unity.

#### **Jitter**

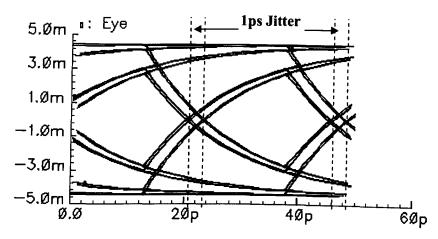

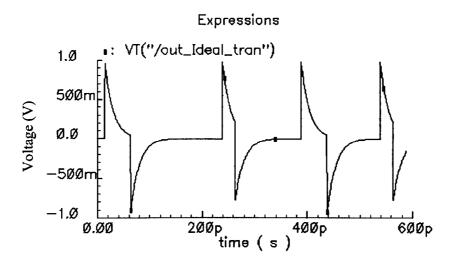

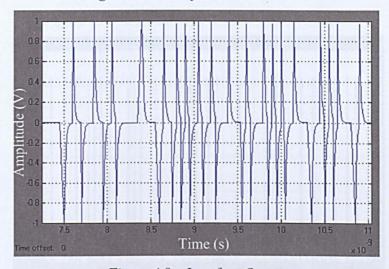

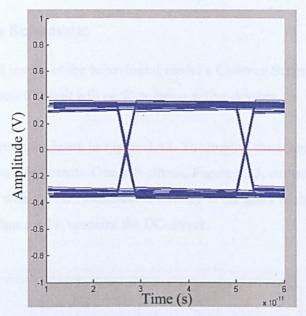

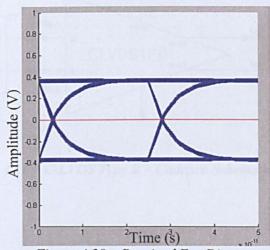

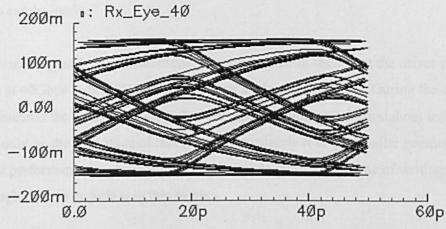

Jitter is considered to be the most important form of noise in terms of SerDes and is regularly used in terms of merit for components destined for SerDes. Jitter is noise in the time domain [14], therefore its effects are best seen in the transient response of the system. Figure 2.6 was produced in Cadence by the author to show how jitter can be seen in an 'eye-diagram'.

Figure 2.6 – Simulated eye-diagram showing jitter noise

From the eye-diagram above it can be noted that the pulse does not always cross the zero crossing point at the same point in time. This spread is called Jitter.

Jitter can be caused at any stage of the system, but the largest contributors are from the PLL, inter-symbol interference and impedance mismatching [15]. Because of this the Total Jitter (TJ) can be split into 2 main groups, namely (i) Deterministic Jitter, (ii) Random Jitter [16].

Deterministic Jitter (DJ) is predictable by definition and covers Data Dependent Jitter (DDJ) and Phase Jitter (PJ) [17]. DJ can be caused by clock noise, power supply noise, process variations and Inter Symbol Interference (ISI). DJ is bounded in nature and therefore has a maximum value.

Random Jitter (RJ) is random by definition. It can take Gaussian distribution form however other forms also may be observed. Random Jitter is usually caused by device noise i.e. Shot, Flicker and Thermal noise are the common contributors to RJ [18]. RJ is unbounded in nature and hence the peak value depends on the length of time over which it is measured. This noise is the main cause of the bit error rate of SerDes links.

#### 2.2.4 Channel Characteristics and Equalisation

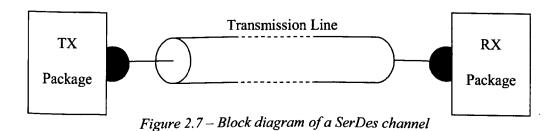

As SerDes is designed for wired transmission the "Channel", Figure 2.7, consists of the "package", which is the capacitance and resistance associated with the signal leaving the package. The transmission line which can be the wire, the track or the backplane and the associated parasitics of each, ending with another package which represents the receiver's physical package properties.

It is important to be able to include the extra parasitics associated with the channel into the simulation as it will give more accurate physical limitations to the simulation. As the transmission line is the biggest limiter of performance lots of research is done on improving its properties and so it can be assumed that there will be sufficient improvements to transmission line technology that the transmission line will be a suitable medium for the target speeds. As a rule of thumb the worst case scenario would be -25dB of signal attenuation at 20GHz which is the equivalent of about 8 inches of PCB made out of FR4 material or 16inches of PCB made out of Rogers material.

However to keep simulations as accurate as possible TI have created S-Parameter files that accurately simulate the channel and are adaptable to future improvements of process technologies. Due to complicated legal issues these S-Parameter files have to remain on TI's servers therefore a lumped approximation is needed for simulations of the IBM transistor models which are run locally.

#### Expressions

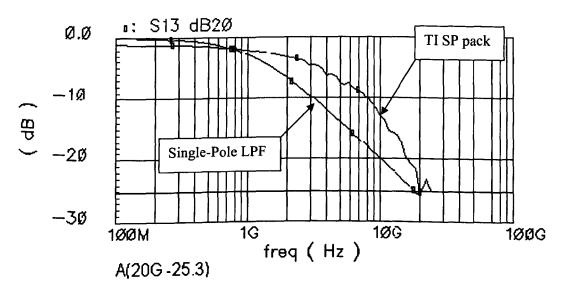

Figure 2.8 - Simulated SerDes channel characteristics

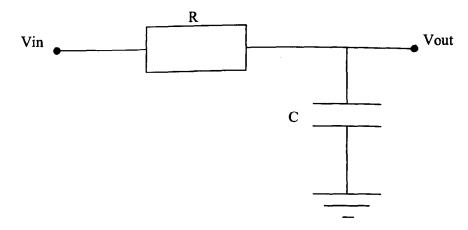

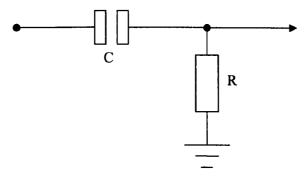

The channel, whose characteristics are shown in Figure 2.8, effectively behaves as a low pass filter and as a first order approximation can be considered as a single pole RC filter [19], Figure 2.9. It is known that the resistance of the transmission line is  $50\Omega$  and using  $f = \frac{1}{2\pi RC}$  an appropriate capacitance can be selected for the appropriate frequency. For comparison the LPF attenuation characteristic is also shown in Figure 2.8.

Figure 2.9 - Lumped sum approximation of a channel

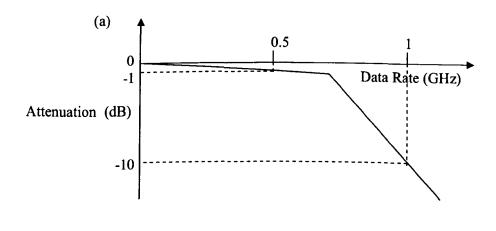

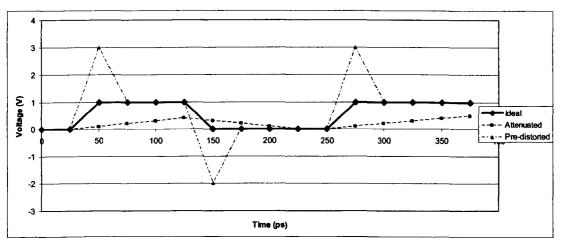

De-emphasis is a method that is used to balance the attenuation of the channel, which is a form of equalisation. It works by purposely attenuating the low frequency components of the signal by adding a high pass filter to the low pass filter which gives an attenuation curve similar to the one in Figure 2.10

Figure 2.10 – Attenuation curves of transmission line, channel attenuation (a), result of de-emphasis (b)

It can be seen from Figure 2.10 that the difference in attenuation between the 0.5GHz signal and the 1GHz signal has been greatly reduced by using de-emphasis. This form of equalization has a profound effect on increasing signal integrity and is widely used in modern communication systems.

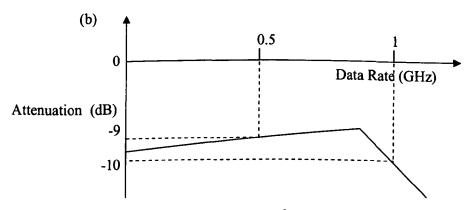

Pre-emphasis is essentially the opposite of de-emphasis wherein instead of attenuating low frequencies the high frequencies are boosted to compensate for the high frequency losses of the channel. Figure 2.11 shows how pre-emphasis can be used to increase the bandwidth of the transmission line. This makes for a more efficient use of power, by not wasting power by attenuating the low frequencies, however this technique is not widely adopted as the transistors need to be overdriven during high frequency cycles.

Figure 2.11 –Pre-emphasis

The next chapter will review various line driver architectures with the aim to identify which architecture is best suited to the high-speed low-voltage environment.

#### 2.3 References

- [1] J.C. Chen, 'Multi-Gigabit SerDes: The Cornerstone of High Speed Serial Interconnects', http://www.design-reuse.com/articles/10541/multi-gigabit-serdes-the-cornerstone-of-high-speed-serial-interconnects.html, accessed December 2006.

- [2] M. Harwood, et al, 'A 12.5Gb/s SerDes in 65nm CMOS Using a Baud-Rate ADC with Digital Receiver Equalization and Clock Recovery', 2007 IEEE International Solid-State Circuits Conference 24.1, 2007, pp.436 437.

- [3] E.H. Suckow, 'Basics of High-Performance SerDes Design, Part I & II', http://www.analogzone.com/iot\_0414.pdf, accessed January 2007.

- [4] J. Zhang, Z. Wong, 'White Paper on Transmit Pre-Emphasis and Receive Equalization', http://www.analogzone.com/io\_shoot\_mindspeed.pdf, accessed Febuary 2007.

- [5] C. Huang, J. Lain, 'FPCM-Assisted Blind Channel Equalization of M-QAM Signals for Time-Varying Channels', IEEE International Conference Proceedings on Networking, Sensing and Control, 2007, pp.787 - 791.

- [6] H. Kwong, et al., 'Embedded preemphasis and deemphasis circuits',U.S. Patent 6 975 517, 30 May, 2005.

- [7] C. Tidestav, et al, 'Realizable MIMO Decision Feedback Equalizers: Structure and Design', IEEE Transactions on Signal Processing Vol. 49, 2001, pp.121 133.

- [8] 'Telecommunications: Glossary of Telecommunication Terms', Federal Standard 1037C, http://www.its.bldrdoc.gov/fs-1037/fs-1037c.htm, accessed January 2007.

- [9] H. Boezen, 'Can Bus Driver with Symmetrical Differential Output Signals',U.S. Patent 6 154 061, 28 Nov, 2000.

- [10] Intel, 'Differential Signaling', download.intel.com/education/highered/signal/ELCT865/Class2\_10\_11\_12\_Diffe rential\_Signaling.ppt, accessed January 2007.

- [11] Lattice, 'Differential Signaling', Application Note AN6019, http://www.latticesemi.com/lit/docs/appnotes/pac/an6019.pdf, accessed January 2007.

- [12] P.R. Gray, et al, Analysis and Design of Analog Integrated Circuits, Forth Edition, ISBN:0-471-32168-0, 2001.

- [13] C. Bowick, 'RF Circuit Design', ISBN: 0-7506-9946-9, 1982, pp.176.

- [14] M. Ishida, et al, 'A Method for Testing Jitter Tolerance of SerDes Receivers

Using Random Jitter,' in Proc. Int. Engr. Consortium DesignCon 2007, January,

2007.

- [15] B. Katz, 'Mastering Audio, the art and the science', ISBN: 0-2408-0545-3, 2002.

- [16] "Fiber Channel Methodologies for Jitter and Signal Quality specification (MJSQ)", National Committee for Information Technology Standardization (NCITS), 2001.

- [17] A. Neves, 'Methods for Extracting Deterministic Jitter in Passive Physical Systems', Teraspeed Consulting Group LLC, 2006.

- [18] A. Kuo, et al, 'Jitter Models and Measurement Methods for High-Speed Serial Interconnects', IEEE Test Conference Proceedings, 2004.

- [19] Mike Harwood, 'Real FR4 micro-strip channel responses and the improvement from a first-order, single-zero equalizer', Inphi, unpublished.

# Chapter 3

# **Critical Review of Line Driver Topologies**

| 3.1 Introduction                               | 2 |

|------------------------------------------------|---|

| 3.2 Device Parameters                          |   |

| 3.3 Current Mode Logic                         |   |

| 3.4 Low Voltage Positive Emitter Coupled Logic |   |

| 3.5 H-Bridge                                   |   |

| 3.6 Low Voltage Differential Signalling        |   |

| 3.7 Conclusion.                                |   |

| 3.8 References                                 |   |

#### 3.1 Introduction

In this chapter, four of the most frequently used line drivers will be presented and critically analysed. This will provide a sound knowledge base of existing line driver architectures to enable the development of two new line drivers that are presented in Chapter 4.

To ensure an accurate comparison can be made, each circuit in this chapter will be tested under the same conditions. The input signal will be a differential signal in all cases, generated by two voltage pulse generators in anti-phase. A differential signal is used to increase the resilience of the driver to noise by only amplifying the voltage difference between the two signals, as explained in Chapter 2. Any noise from previous stages will appear equally on both inputs and therefore the difference between the outputs will remain essentially the same. Similarly the drivers will all use a differential output stage, which will protect the transmitted signal from noise such as electromagnetic interference applied to the transmission line by using the same principle [1]. Also all circuits will be simulated under ideal conditions where all parasitics are ignored, and it will be assumed that the driver will have perfect impedance match with the transmission line with zero capacitance load.

In addition all circuits presented in this chapter are tested to determine how well they each conform to the respective governing standards, which are summarised in Table 3.1.

| Parameter       | CML        | LVPECL | LVDS  |

|-----------------|------------|--------|-------|

| V <sub>OH</sub> | VDD        | 2.3V   | 1.425 |

| $V_{OL}$        | VDD - 0.8V | 1.6V   | 1.075 |

| $V_{OD}$        | 800mV      | 700mV  | 350mV |

| V <sub>CM</sub> | VDD - 0.4V | 1.95V  | 1.25V |

| $R_T$           | 50Ω        | 50Ω    | 100Ω  |

Table 3.1 – Standard Specifications

Key:

VDD = Positive Power Supply

CML = Current Mode Logic

LVPECL = Low-Voltage Positive Emitter Coupled Logic

LVDS = Low-Voltage Differential Signalling

$V_{OH} = Output Voltage (High)$

V<sub>OL</sub> = Output Voltage (Low)

V<sub>OD</sub> = Differential Output Voltage Swing

V<sub>CM</sub> = Common Mode Voltage

RT = Termination Resistance

CML is a style of interface but for the purpose of this comparison the CML standard is taken from the requirements of Clause 47 of the IEEE 802.3 standard which defines the physical layer of the XAUI interface [2]. LVPECL's standard can be found in TIA's ANSI/TIA/EIA-613 [3]. Finally the LVDS standard can be found in ANSI/TIA/EIA-644-A [4]. It should be noted that all of the standards, except for CML, shown in Table 3.1 require power supply voltage levels above 1.6V. Therefore these circuits will be simulated in Cadence Capture using the IBM T68A 130nm CMOS transistor which is rated to work at these voltage levels.

#### 3.2 Device Parameters

To determine the primary design equations for the various line driver topologies it is necessary to extract the main device parameters from the simulation model, namely:

- V<sub>T</sub>, threshold voltage.

- I<sub>D</sub> V<sub>DS</sub> curves.

- $\lambda$ , channel length modulation parameter.

- f<sub>T</sub>, transition frequency.

- μnCox, a product of electron mobility and capacitance of oxide per unit length.

The following section will put the IBM model under various tests designed to extract the above mentioned parameters.

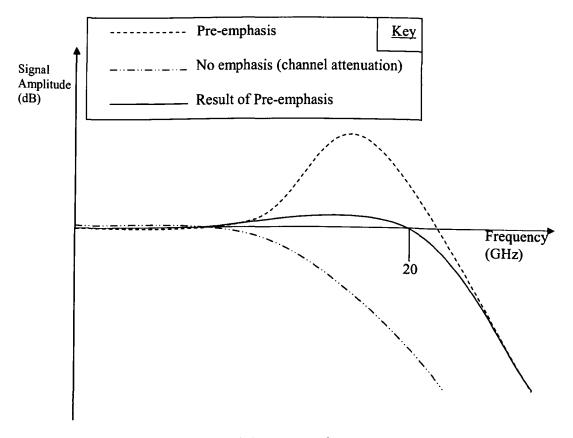

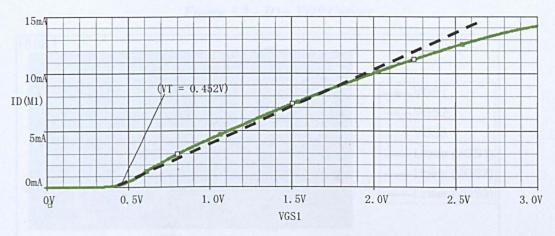

The threshold voltage can be obtained by applying an increasing DC voltage between gate and source of a MOSFET and observing when the transistor conducts significantly [5], an easy method to ensure that the results are consistent is to use a linear extrapolation back to the zero crossing of the y axes. Figure 3.1 shows the circuit and Figure 3.2 shows the results of the  $V_T$  test. Looking at the curve in Figure 3.2 it can be seen that  $I_D$  increases significantly at  $V_{GS} = 0.45V$ , hence  $V_T = 0.45V$ .

Figure 3.1 – Test circuit to find  $V_T$

Figure 3.2 -Results of V<sub>T</sub>Test

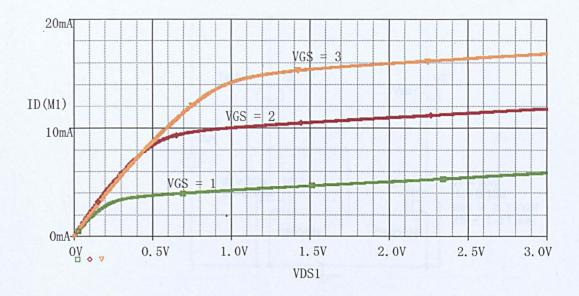

Using the same circuit in Figure 3.1  $I_D \sim V_{DS}$  curves can be obtained by running a parametric  $V_{GS}$  with a DC sweep of  $V_{DS}$  [6]. The results obtained are shown in Figure 3.3. Normally the  $\lambda$  parameter can be obtained by extrapolating the (almost) horizontal area of the curve. However, one effect of such short channel MOSFETs is that the extrapolations no longer converge on a single voltage, as shown in Figure 3.4.

Figure 3.3 – ID – VDS Curves

Figure 3.4 – The effect of channel length modulation on the Early Voltage

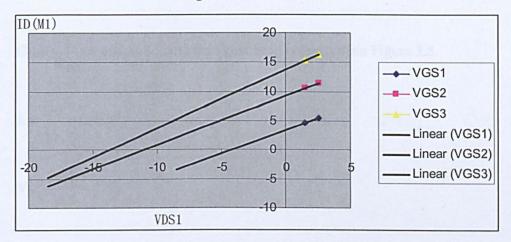

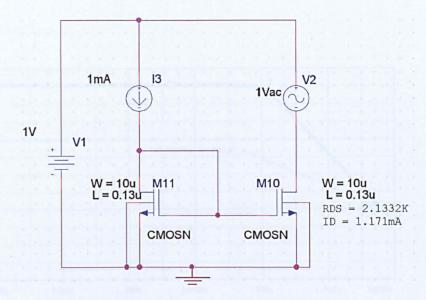

From Figure 3.4 it can be seen that the early voltage  $(V_A)$  [7] changes with different levels of  $V_{GS}$ . Therefore  $\lambda$  needs to be calculated by different means. From device physics we know that  $Go \approx \lambda \times I_D$  [8], where Go = output conductance, therefore using a simple current mirror, Figure 3.2.5, the output conductance (Go) can be calculated for a known drain current  $(I_D)$ .

Figure 3.5 – Simple Current Mirror to calculate R<sub>DS</sub>

$$Go = \frac{1}{R_{DS}} = 468.8 \text{uS}$$

, and the value of  $I_D$  is taken from Figure 3.5 (3.1)

$$\lambda = \frac{\text{Go}}{\text{I}_{\text{D}}} = 0.4\text{V}^{-1} \tag{3.2}$$

$$V_A = \frac{1}{0.4} = 2.5V$$

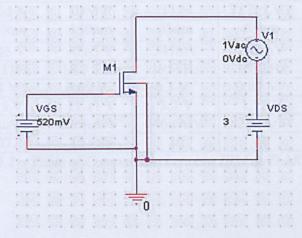

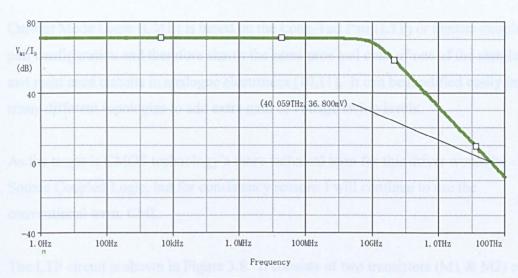

The  $f_T$  is a measure of the maximum useful frequency of the transistor when used as an amplifier [8], the  $f_T$  of the MOSFET is found by using the circuit in Figure 3.6. The impedance of the drain is measured in an AC sweep and  $f_T$  is the frequency where the impedance is unity (0dB), Figure 3.7, measured to be 40THz.

Figure 3.6 -  $f_T$  Schematic

Figure 3.7 - Transition Frequency (FT)

And finally, the µxCox parameter can be found by calculation [9], using the equation:

$$I_{D} = \frac{\mu x \text{Cox}}{2} \frac{W}{L} (V_{GS} - V_{T})^{2}$$

(3.3)

:. where  $\mu x = \mu n$  or  $\mu p$  (nMOS or pMOS)

$$\mu x \text{Cox} = \frac{2I_{D}}{\frac{W}{L} (V_{GS} - V_{T})^{2}}$$

(3.4)

These parameters were also found for the P-channel and N-channel IBM transistors as well as the TI transistors, two of which are the standard 65nm transistor, and two special transistors with a low  $V_T$ . These results are shown in Table 3.2 for comparison and reference purposes.

| Parameter        | IBM N               | IBM P                | TIN                  | TI N LVT             | TIP                  | TIPLVT               |

|------------------|---------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| L(min)           | 130nm               | 130nm                | 65nm                 | 65nm                 | 65nm                 | 65nm                 |

| $V_{\mathrm{T}}$ | 0.45 V              | -0.65 V              | 341mV                | 292mV                | -375mV               | -312mV               |

| $f_T$            | 40 THZ              | 18.7 THz             | 195THz               | 163THz               | 96.5THz              | 95THz                |

| λ                | 0.4 V <sup>-1</sup> | 0.09 V <sup>-1</sup> | $0.3 \text{ V}^{-1}$ | 0.87 V <sup>-1</sup> | 0.93 V <sup>-1</sup> | 0.44 V <sup>-1</sup> |

| $V_A$            | 2.5 V               | 11.11 V              | 3.3 V                | 1.15 V               | 1.1 V                | 2.27 V               |

| μхСох            | $186\mu A/V^2$      | $226\mu A/V^2$       | $646\mu A/V^2$       | $823\mu A/V^2$       | $554\mu A/V^2$       | $476\mu A/V^2$       |

| W/L              | 107.7               | 153.85               | 10                   | 10                   | 20                   | 20                   |

Table 3.2 - Table of Comparison between IBM & TI MOSFETS

# 3.3 Current Mode Logic

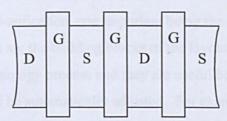

Current Mode Logic (CML) is based on the Long-Tail Pair (LTP) or emitter-coupled pair configuration and therefore shares the same pros and cons of one of the simplest and most used circuits in analogue electronics [10,11]. It can be modified easily into many different topologies to add extra gain or voltage swing levels.

As the target is CMOS technology a more technical term for this driver would be Source Coupled Logic, but for consistency reasons I will continue to use the conventional term, CML.

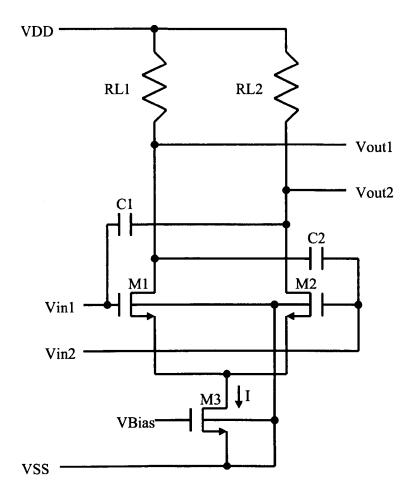

The LTP circuit is shown in Figure 3.8. It consists of two transistors (M1 & M2) each loaded by a resistor (RL1 & RL2) on the drain. Another transistor (M3) is used to provide the bias currents for the transistors.

Figure 3.8 – CML driver configuration

The drain of M3 provides a high impedance node for the signal and due to the input being of a differential nature only one half of the long-tail pair will be active making the equivalent circuit a common source amplifier where:

$$Vout = -gmVin(RDS//RL)$$

(3.5)

$$Rout = \frac{Vout}{Iout} = RDS//RL$$

(3.6)

$$Rin = \infty$$

&  $Ai = \infty$

To reduce the complexity of the schematic RL1 and RL2 represent termination with an ideal matched transmission line. The value of RL is fixed at  $50\Omega$  to provide impedance matching to the transmission line. This is one of the obvious drawbacks as this reduces the available voltage output swing.

The standard of CML, taken from Clause 47 of the IEEE 802.3 standard, states the differential output swing is  $800\text{mV}_{P-P}$  and to relate to the next type of driver which is called the 'Low Voltage Positive Emitter Coupled Logic' (LVPECL) VDD will be set at 3.5V. The following equations define the parameters of I, M1, M2 of Figure 3.3.1.

$$Vout=VDD-0.8V = 3.5-0.8 = 2.7V$$

$$AV = -gmRL' \qquad Where: \\ AV = Votage \ Gain \\ RL' = RDS//RL \\ K = \mu nCox \qquad (3.7)$$

rearranging for  $\frac{W}{L}$  gives

$$AV = \sqrt{\frac{W}{L}} \times 2\sqrt{\frac{K}{2}} ID \times RL'$$

(3.9)

$$\frac{AV}{2\sqrt{\frac{K}{2}ID} \times RL'} = \sqrt{\frac{W}{L}}$$

(3.10)

$$\frac{W}{L} = \left[ \frac{AV(RL + R_{DS})}{2\sqrt{\frac{K}{2}} ID \times RL \times R_{DS}} \right]^{2}$$

$$= \left[ \frac{0.9(50 + 75)}{2 \times 50 \times 75 \times \sqrt{80 \times 10^{-6} \times 15 \times 10^{-3}}} \right]^{2}$$

$$= 187.5$$

(3.11)

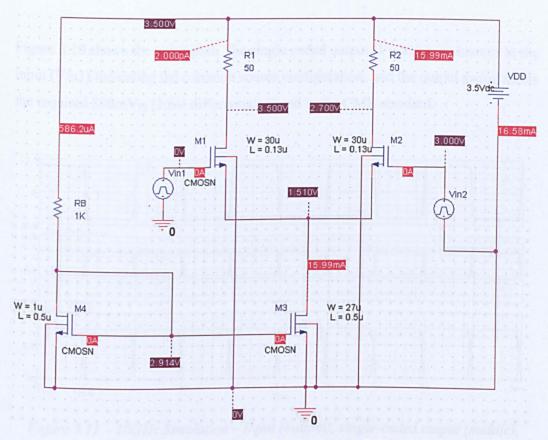

$$\frac{\mathbf{W}_{1\&2} = 187.5 \times \mathbf{L} = 25 \mu \mathbf{m}}{\mathbf{I} = 15 \mathbf{m} \mathbf{A}}$$

The current, I, is set up using a simple current mirror. The schematic used in testing is show in Figure 3.9. To minimise power consumed by the current mirror the width of the current source transistor M4 has been scaled down by a factor of 27, this reduces the current flowing through M4 to 556µA from 15mA. The length of transistors M3 & M4 are increased to 0.5µm to improve the stability of the current mirror, in turn improving the common mode rejection ratio (CMRR) of the long tail pair.

Figure 3.9 - CML Simulator Schematicwith DC Annotation

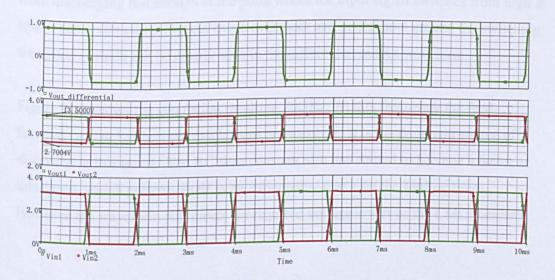

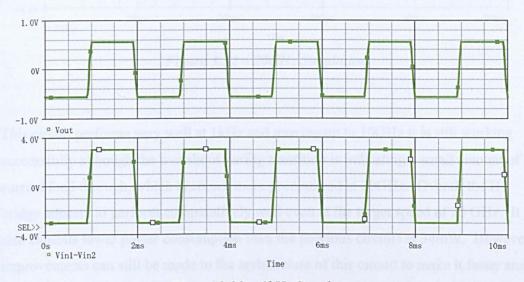

The first simulation will be a 1kHz test signal, shown in Figure 3.10. The purpose of this slow speed test is to ensure the circuit is operating at the required conditions before a high speed signal is applied.

Figure 3.10 - 1kHz Test Signal – Input (bottom), single-ended output (middle), differential output (top)

Figure 3.10 shows the test signal. The single ended output (Vout1) is an inverse to the input (Vin1) indicating the common source configuration, and the output swing meets the required  $800 \text{mV}_{Pk} (1.6 \text{V differential})$  stated in the CML standard.

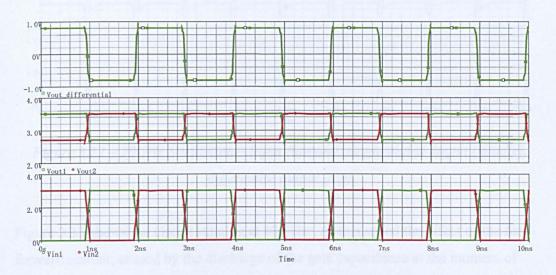

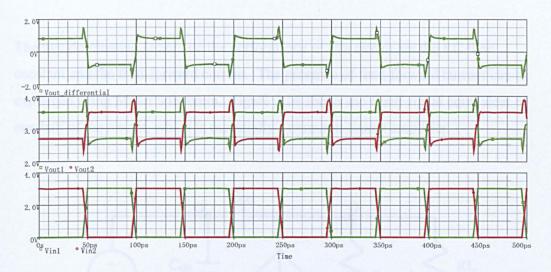

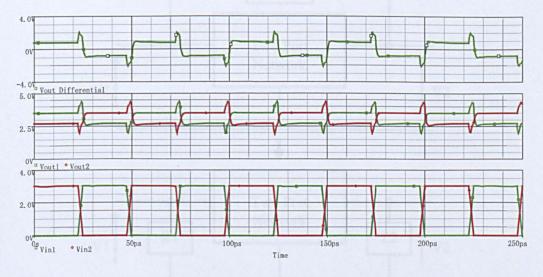

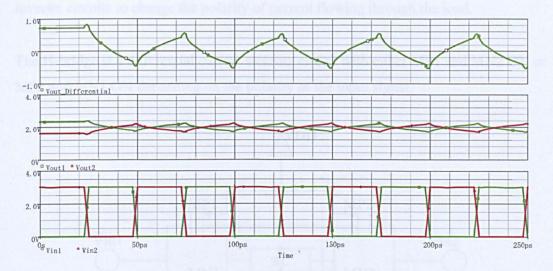

Figure 3.11 – 10GHz Simulation – Input (bottom), single-ended output (middle), differential output (top)

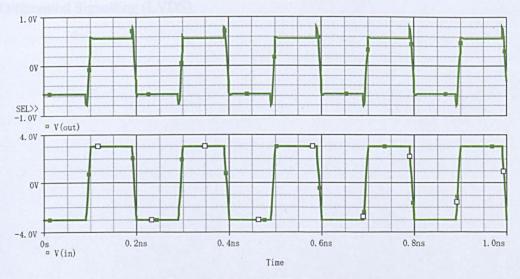

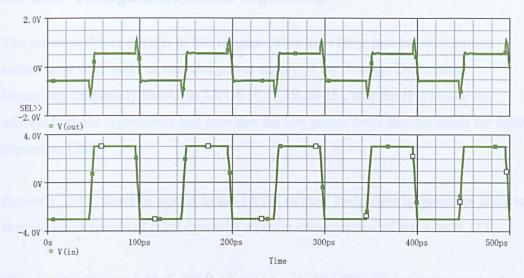

Figure 3.11 shows that CML will still work well at 10 GHz because the output signal swing still meets the  $800 \text{mV}_{Pk}$  standard. There is a slight amount of feed-forward current which is produced by the parasitic capacitances, which prevents the transistor from discharging fast enough at the point where the input signal switches from high to low. These extra current spikes cause overshoot and undershoot around the switching transitions, which can be clearly seen in the differential output waveform.

Figure 3.12 shows the simulation results at 20GHz. At this frequency the feed-forward current has become much more pronounced. It is the dominant source of distortion at this speed. The RC time constant also has started to become a factor at this speed, which presents itself as an exponential curve on the settling times. However the waveform still meets the required voltage levels of the CML standard.

Figure 3.12 – 20GHz Simulation – Input (bottom), single-ended output (middle), differential output (top)

Figure 3.13 shows the circuit running at 40GHz. At this speed the effect of the feed-forward current, caused by the discharge of the gate capacitance at the moment of switching, coupled with the RC time constant has pushed the output voltages out of the standard mode of operation; this could cause the receiver to reject the signal. At some points the differential voltage reaches 2V which is over double the specified limit. Due to the feed-forward current distortion presented on the output voltage levels, the circuit no longer conforms to the defined standard and therefore is deemed not suitable for operation at 40GHz.

Figure 3.13 – 40GHz Simulation – Input (bottom), single-ended output (middle), differential output (top)

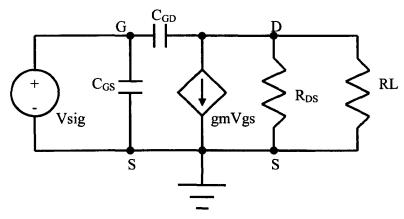

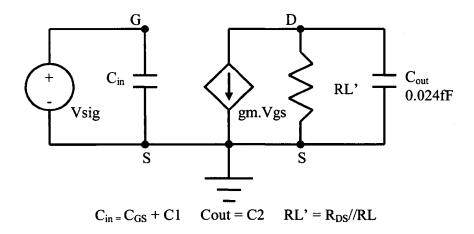

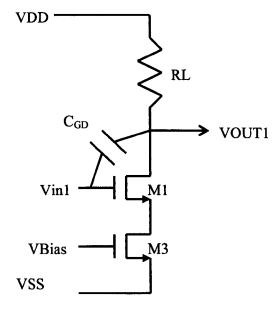

The two dominating factors on the performance of this circuit are the RC time constant and the feed-forward current. The presence of feed-forward current can be explained using Miller's theorem. Figure 3.14 shows the small signal equivalent of one half of the circuit, which is essentially a common source amplifier.

Figure 3.14 – Small Signal Analysis [12]

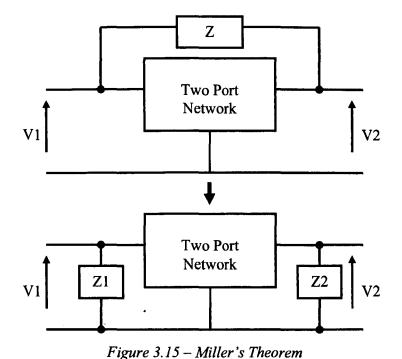

Miller's theorem states that impedance, Z, connected across the input and output of a linear two port network will have an equivalent circuit of separate input and output impedances, Z1 and Z2, [13]. This is better illustrated in Figure 3.15

$$Z1 = \frac{Z}{1 - A}$$

and  $Z2 = \frac{Z}{1 - \frac{1}{A}}$  where A = Gain (3.12)

Looking back to Figure 3.14 it can be seen that capacitor  $C_{GD}$  is connected between the Gate (input) and Drain (output), therefore Miller's theorem can be applied. Z1 and Z2 can be calculated using the following equations:

$$C_{GD} = CGDO(W_{eff})$$

$$= (3.98E - 10)(30E - 6)$$

$$= 0.012fF$$

Where:

$$CGDO = capacitance per unit$$

$$W_{eff} = effective transistor width$$

(3.13)

$$C1 = C_{GD} (1 - gm(RL // R_{DS}))$$

(both taken from transistor model) (3.14)

$$=0.012\times10^{-12}\left(1-\left(2\sqrt{\frac{K}{2}\frac{W}{L}I_{D}}\right)\left(\frac{50\times74}{50+74}\right)\right)=0.012\times10^{-12}\left(1-\left(0.03437\times30\right)\right)$$

=0.0004fF

and

$$C2 = C_{GD} \left( 1 - \frac{1}{gm(RL//R_{DS})} \right)$$

$$=0.012\times10^{-12}\left(1-\frac{1}{\left(2\sqrt{\frac{K}{2}\frac{W}{L}}I_{D}\right)\left(\frac{50\times74}{50+74}\right)}\right)=0.012\times10^{-12}\left(1+\frac{1}{(0.03437)(30)}\right)$$

$= \underline{0.024 \text{fF}}$

Figure 3.16 - Small Signal Analysis with Miller's Theorem Applied

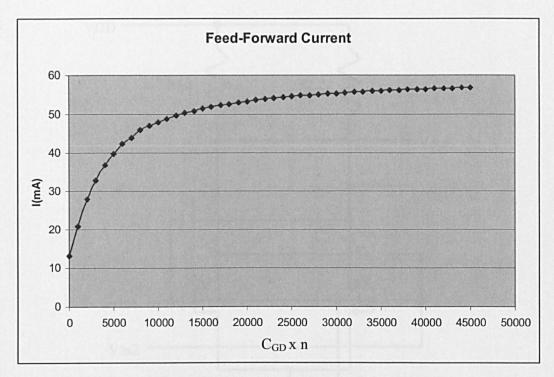

Figure 3.16 now shows the appearance of a capacitor on the load which is the dominant source of the RC time constant and the feed-forward current. This model is just used as a graphical representation. Due to the very high frequency used in simulation a much larger, more complicated model is needed to simulate an equivalent circuit. Due to the complexity of the model another way to show the effect of  $C_{GD}$  on the feed-forward current is to increase  $C_{GD}$  by adding a capacitor from the Gate to the Drain. Figure 3.17 shows the circuit used to obtain the results by multiplying the capacitor  $C_{GD}$  by the factor n and recording the amount of feedthrough current shown in Figure 3.18, which shows the graphical representation of the results.

Figure 3.17 – Feed-Forward Current Test Circuit

Figure 3.18 – Graph of Feed-Forward Current vs. C<sub>GD</sub>

The results clearly show a correlation between C<sub>GD</sub> and the amount of feed-forward current.

A common technique employed in amplifier design is capacitance neutralisation [14]. The schematic of the 'neutralised' circuit is shown in Figure 3.19. The two capacitors, C1 and C2, counteract the Miller capacitance by providing equal but opposite currents to counteract the flow of current leaking through the gate of the transistor.

The design values for the circuit in Figure 3.19 are:

- VDD = 3.5V

- VSS = 0V (ground)

- $RL1 = RL2 = 50\Omega$

- $Vin1 = 3V_{p-p}$ , 0° phase, square wave

- $Vin2 = 3V_{p-p}$ ,  $180^{\circ}$  phase, square wave

Figure 3.19 - CML with Capacitive Neutralisation [15]

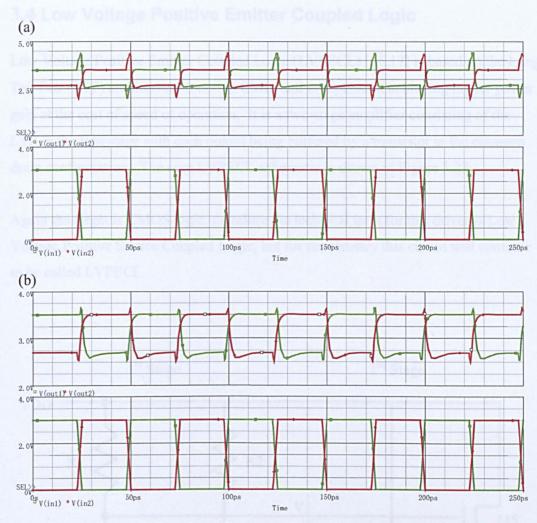

This circuit was then converted to a 'Capture schematic', Figure 3.20, for simulation using the same design values as CML. A comparison of results can be found in Figure 3.21. Comparing CML with and without this neutralisation technique indicates a noticeable improvement in the feed-forward current when capacitance neutralisation is employed.

Capacitors C1 and C2 can be matched easier by using identical devices[15], where their Gate and Source will be connected to the input and the Drain will connect to the opposite output, as shown in Figure 3.20. This will not provide an exact match due to different biasing but will be very accurate.

Figure 3.20 – Neutralised CML Schematic

Figure 3.21 – CML without Capacitive Neutralization (a), with Capacitive Neutralization (b)

The chip area of the un-neutralised CML was 46 um<sup>2</sup> and power consumption was 64.0mW. By comparison the neutralised CML chip area increased to 61.6 um<sup>2</sup>, and the power consumption remained unchanged. The neutralisation capacitors have dramatically reduced the signal spikes caused by feed-forward current, although not completely due to the slight biasing differences between the original transistor and neutralisation transistor causing a slight mismatch in capacitance. The drawback of adding the neutralisation capacitors adds to the load capacitance that the transistor needs to drive and therefore reducing the edge rate.

## 3.4 Low Voltage Positive Emitter Coupled Logic

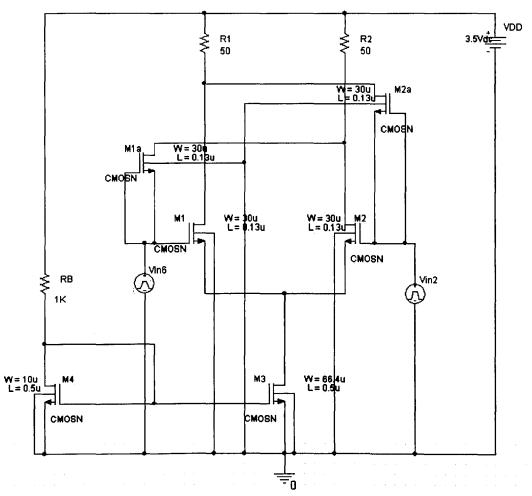

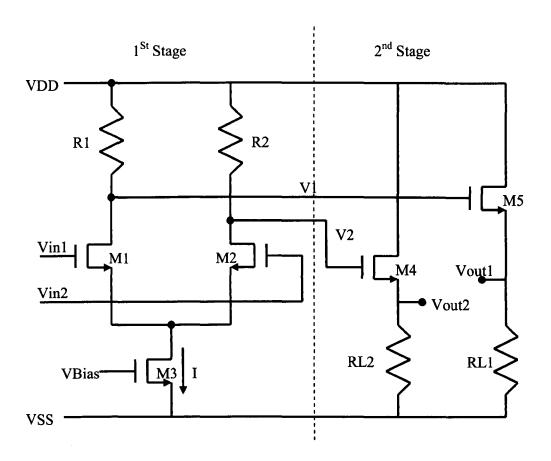

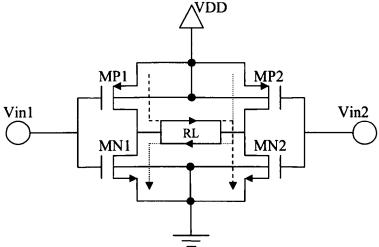

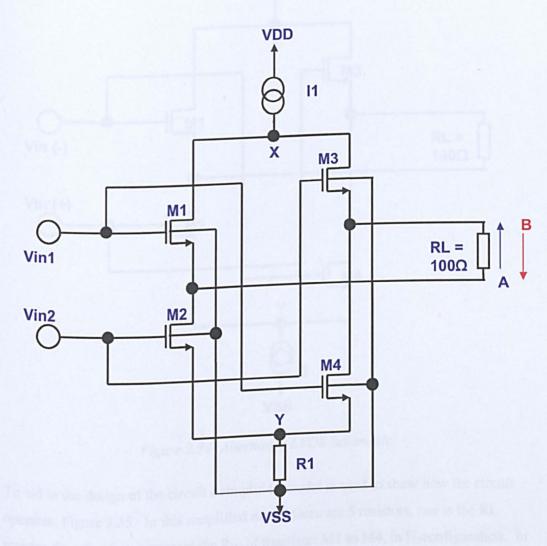

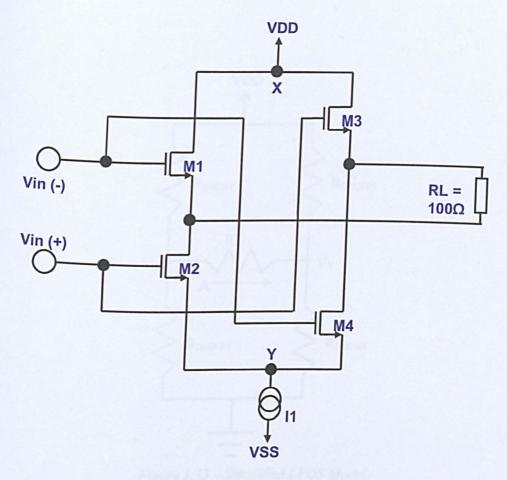

Low Voltage Positive Emitter Coupled Logic (LVPECL) [16,17] is based on the Long Tail Pair (LTP) architecture found in CML, and is capable of achieving higher power gain at the cost of speed of operation. It is a two-stage amplifier consisting of the LTP in the first stage with each output being buffered by a transistor in the common drain configuration. The core LVPECL schematic is shown in Figure 3.22.

Again the target is CMOS logic, therefore the technical term for this driver is Low Voltage Positive Source Coupled Logic, but for consistency this circuit will continue to be called LVPECL.

Figure 3.22 – LVPECL Schematic

The common drain amplifier, also known as the source follower, provides a high input impedance and low output impedance unity voltage gain, Av=1, with a large current gain. The first stage of the amplifier behaves exactly the same as in the CML driver. However this time the outputs are tailored to drive the second stage common drain amplifier rather than a transmission line directly as in the CML. As the common drain amplifier acts as a buffer, this means that resistors R1 and R2 can now be higher than  $50\Omega$  and they will not affect the output impedance of the circuit, therefore the first stage can now be designed more efficiently.

The second stage of the amplifier, the source follower, has an open-loop voltage gain given by

$$Avo = \frac{Ro}{Ro + \frac{1}{gm}}$$

(3.15)

where Avo is the open-circuit voltage gain, Ro is the unloaded output resistance and gm is the transconductance of the output stage transistors[12].

Usually Ro >> 1/gm and so the source follows the gate, hence the name source follower. However, due to the short length of the transistor used Ro is going to be a lot smaller than usual, perhaps 10s of Ohms instead of 100s of kOhms, hence the voltage gain will be significantly less than 1 so the full equation must be used to accurately model the source follower.

When the load is added the voltage gain becomes

$$Av = \frac{RL//Ro}{(RL//Ro) + \frac{1}{gm}}$$

(3.16)

where Av is the voltage gain

According to the standards, shown in Table 3.1 for LVPECL,  $V_{OH} = 2.3V$  and  $V_{OL} = 1.6V$ . The calculations below show the design parameters needed to achieve these standards.

$$\frac{\text{Vout}}{\text{Vin}} = \frac{\text{RL}//\text{Ro}}{(\text{RL}//\text{Ro}) + \frac{1}{\text{gm}}} \qquad \text{Let RL}//\text{Ro} = \text{RL' and gm} = 2\sqrt{\frac{\text{K}}{2} \frac{\text{W}_s}{\text{L}}} \text{ID}$$

(3.17)

$$=\frac{RL'}{RL'+\frac{1}{2\sqrt{\frac{K}{2}\frac{W_5}{L}ID}}}$$

(3.18)

$$\frac{Av}{1} = \frac{RL'}{RL' + \frac{1}{\sqrt{\frac{W_5}{L}}} \cdot \frac{1}{\sqrt{2K \cdot ID}}}$$

(3.19)

Rearrange for RL'

$$RL' = Av \bullet RL' + Av \bullet \sqrt{\frac{L}{W_5}} \bullet \frac{1}{\sqrt{2K \bullet ID}}$$

(3.20)

Divide both sides by RL'+AV

$$RL'(1-AV) = Av \bullet \sqrt{\frac{L}{W_5}} \bullet \frac{1}{\sqrt{2K \bullet ID}}$$

(3.21)

Rearrange to find W,

$$\sqrt{\frac{L}{W_s}} = \frac{RL'(1-Av)}{AV \bullet \frac{1}{\sqrt{2K \bullet ID}}}$$

(3.22)

$$\sqrt{\frac{L}{W_5}} = \frac{RL'(1 - Av)(\sqrt{2K \bullet ID})}{Av}$$

(3.23)

$$\sqrt{\frac{W_5}{L}} = \frac{Av}{RL'(1 - Av)(\sqrt{2K \bullet ID})}$$

(3.23)

$$= \frac{Av(RL + Ro)}{(RL \times Ro)(1 - Av)(\sqrt{2K \bullet ID})}$$

(3.24)

Where:

$$Av = 0.66$$

$$RL = 50$$

$$Ro = 26$$

$$K = 160 \times 10^{-6}$$

$$ID = 50 \times 10^{-3}$$

$$\sqrt{\frac{L}{W_5}} = \frac{0.66(50 + 26)}{50 \times 26(1 - 0.66) \bullet \left(\sqrt{320 \times 10^{-6} \times 50 \times 10^{-3}}\right)} = 28.32$$

$$\frac{\mathrm{W_5}}{\mathrm{L}} = 805$$

$$L = 0.13 \mu \text{m}$$

:  $W_5 = W_6 = 105 \mu \text{m}$

Now the output voltages need to be considered to ensure that the LVPECL stand are met.

$$V_{OL} = Vin = \frac{Vout}{\left(\frac{RL//Ro}{(RL//Ro) + \frac{1}{gm}}\right)} = \frac{Vout}{\left(\frac{RL//Ro}{(RI//Ro) + \frac{1}{2\sqrt{\frac{K}{2}\frac{W_{5}}{L}I_{D}}}}\right)} = V2$$

(3.25)

$$V2 = \frac{1.6}{\left(\frac{17.1}{17.1 + \frac{1}{2\sqrt{80E - 6 \times 805 \times 50E - 3}}}\right)}$$

$$V2 = 2.42V$$

Once the parameters for the second stage have been calculated the next stage is to design the first stage to provide V1=VDD and V2=2.42V

Using equation 3.11 from the previous CML circuit yields

$$\frac{W_1}{L} = \left[ \frac{Av(RL + R_{DS})}{2\sqrt{\frac{K}{2}ID \times RL \times R_{DS}}} \right]^2$$

(3.26)

$$= \left[ \frac{0.81(180 + 300)}{2 \times 180 \times 300 \times \sqrt{80 \times 10^{-6} \times 6 \times 10^{-3}}} \right]^{2}$$

$$=127$$

$$W_1 = W_2 = 4\mu m$$

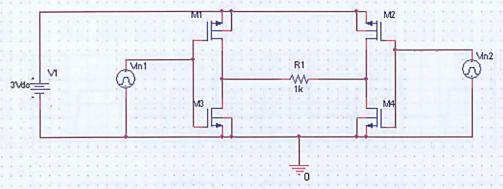

Now all the parameters have been defined a simple current mirror circuit is added (consisting of RB, M4 and M5) to bias the LTP. The schematic for testing is shown in Figure 3.23.

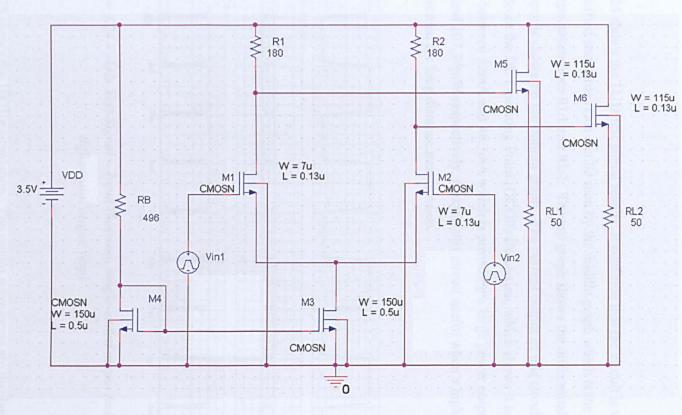

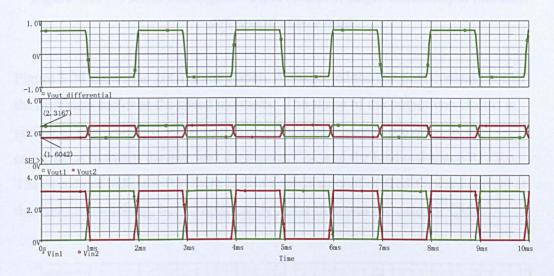

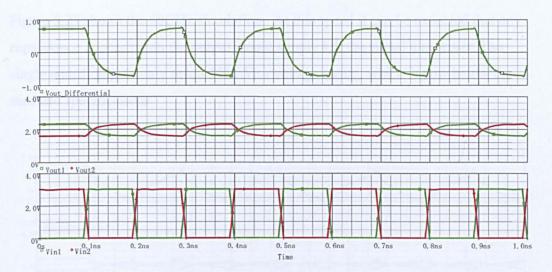

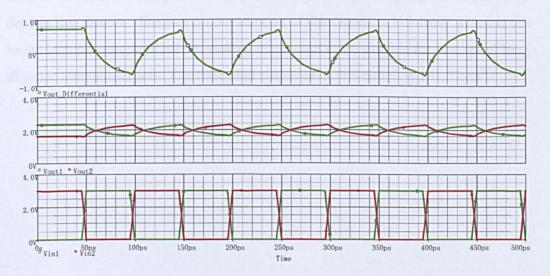

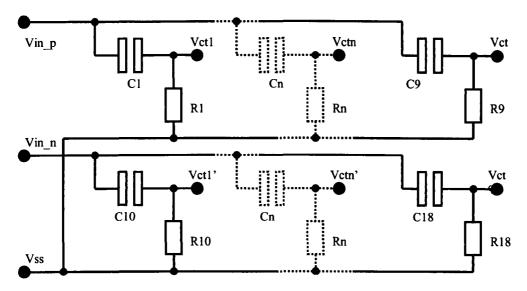

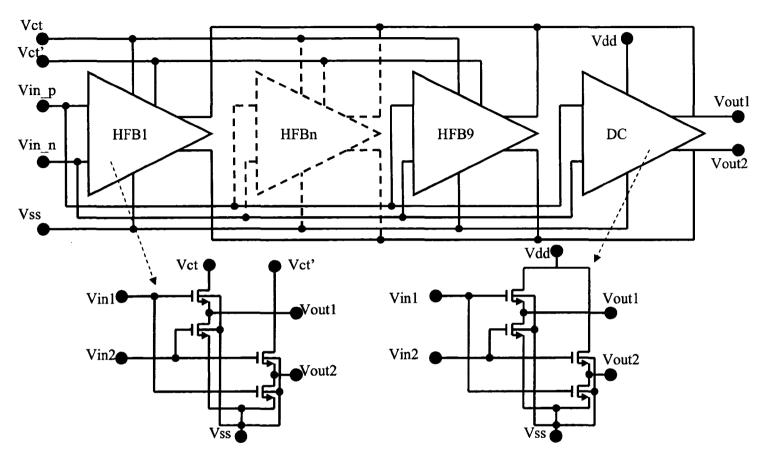

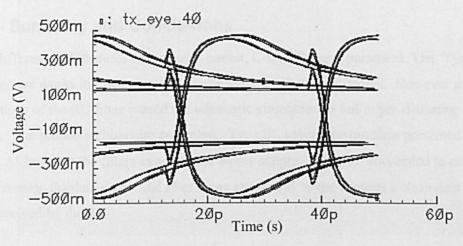

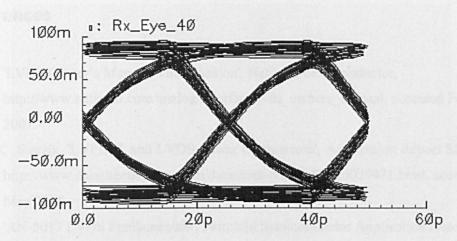

Figure 3.23 - LVPECL Schematic with Annotated Biasing Conditions